Departamento de Engenharia Eletrotécnica

## Mestrado integrado em Engenharia Informática

Sistemas Lógicos – 2º teste (versão A) – 9/12/2015

Duração: 1h20mn | Tolerância: 10mn | Sem consulta

Importante: numere as folhas que entregar (ex. 1 de 4) e identifique-se em todas elas

Responda em folhas separadas aos grupos de questões

## INDIQUE QUAL A PROVA (A ou B) EM TODAS AS FOLHAS QUE ENTREGAR

## Q1 (3 + 3 + 3 valores)

- a) Utilizando um <u>flip-flop do tipo D</u>, apresente, justificando, o circuito necessário para obter um <u>flip-flop do tipo JK</u>.

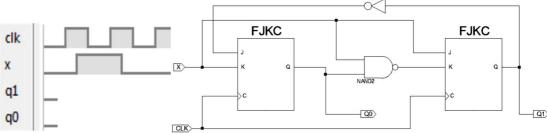

- b) Considere o circuito sequencial síncrono segundo o esquemático abaixo. Tomando o estado inicial Q1Q0=00, complete o diagrama temporal:

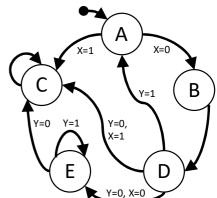

c) Pretende-se desenvolver um sistema para detectar a sequência 01101 presente numa entrada binária X. A saída Z deve tomar o valor 1 quando a sequência é detectada. Considere como de interesse detetar sobreposições entre sequências, isto é, a saída de uma sequência (completa ou parcial) pode contribuir para a sequência seguinte. Apresente um diagrama de estados para o detector de sequência.

## Q2 (3 + 3 + 2 + 3 valores)

Pretende-se projetar um contador síncrono de 3 bits, que contará em módulo 5, utilizando os estados de contagem 0, 1, 2, 4, 5 (em decimal, por esta ordem) e com uma entrada X, que sempre que igual a '1' provoca que o contador salte para o estado de contagem 2. <u>Nota: as saídas, que representam o estado de</u> contagem em binário, coincidem com as variáveis de estado.

- a) Apresente <u>tabela de transição de estados codificados</u>. <u>Importante: considere como don't care as situações não previstas na especificação do contador!</u>

- b) Utilizando flip-flops do tipo D, apresente tabelas de verdade das entradas dos flip-flops, mapas de Karnaugh associados e expressões simplificadas (nota: não necessita apresentar o esquemático do circuito). Importante: considere como don't care as situações não previstas na

especificação do contador!

- c) Considere que o flip-flop associado ao bit mais significativo (i.e. Q2) sofre uma avaria que faz com que a sua entrada permaneça sempre a '0'. Refira, justificadamente, qual seria a agora a sequência de contagem considerando esta situação?

- d) Considere o diagrama de estados da figura imediatamente ao lado. Apresente a tabela de transição de estados, uma codificação de estados possível e a tabela de transição de estados codificados correspondente.