#### Universidade Nova de Lisboa Faculdade de Ciências e Tecnologia Departamento de Engenharia Electrotécnica

# Licenciatura em Eng. Informática

Disciplina de Sistemas Lógicos - 2º teste - 7-7-1999 - 14h

Duração: 1h45mn Tolerância: 15mn Sem consulta

Importante: numere as folhas que entregar (ex. 1 de 4) e identifique-se em todas elas; Responda em folhas separadas aos vários grupos de questões

### **Q1 (2,5 valores)**

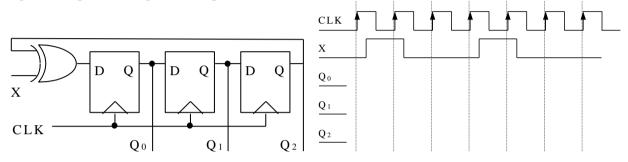

Considere o circuito apresentado na figura utilizando flip-flops sensíveis ao flanco ascendente de relógio. Complete o diagrama temporal:

## Q2 (2 + 2.5 + 1.5 valores)

Pretende-se projectar um contador sínc2rono, com 3 bits, que deverá contar em módulo 6 de acordo com a seguinte sequência (em decimal): 0 2 4 1 3 5. Sempre que o contador esteja no estado que apresenta a saída com valor 1 deverá actuar a saída X com o valor lógico 1.

- a) Apresente tabela de transição de estados e codificação de estados proposta.

- b) Utilizando flip-flops JK, apresente as tabelas das entradas JK e da saída, mapas de Karnaugh associados e expressões simplificadas (não é necessário apresentar o circuito).

- c) Tendo por base a resolução da alínea anterior, diga, justificadamente, para que estado evolui o contador, quando por algum motivo (por exemplo alimentação inicial do circuito) o sistema se encontar no estado 6 (110) ou 7 (111).

# Q3 (2.5 + 1.5 + 2 + 2 valores)

Pretende-se desenvolver um sistema para detectar a sequência 10\*1, em que \* significa zero, uma ou mais ocorrências do símbolo à sua esquerda (por exemplo, 0\* representa uma sequência com zero, um ou mais 0's). A saída Z deve tomar o valor 1 quando a sequência é detectada.

- a) Apresente um diagrama de estados para o detector de sequência.

- b) Obtenha a tabela de transição de estados minimizada utilizando o método da partição.

- c) Apresente a tabela de transição de estados, com os estados codificados.

- d) Utilizando flip-flops D, apresente as tabelas das entradas D e da saída, mapas de Karnaugh associados e expressões simplificadas (não é necessário apresentar o circuito).

### Q4 (2,25 + 1,25 valores)

Considere a seguinte tabela de fluxo de estados de um circuito assíncrono (de que não é fornecida informação adicional).

- a) Obtenha a tabela de fluxo de estados minimizada.

- b) Codifique os estados de modo a evitar corridas.

| X | 0   | 1   |

|---|-----|-----|

| a | a/0 | b/- |

| b | c/- | b/1 |

| c | c/1 | d/- |

| d | e/- | d/0 |

| e | e/- | d/0 |

| f | e/0 | b/1 |