# SISTEMAS DIGITAIS (SD)

#### **MEEC**

#### Acetatos das Aulas Teóricas

Versão 4.0 - Português

#### Aula Nº 23:

**Título:** Máquinas de Estado Microprogramadas: Endereçamento Explícito/Implícito

Sumário: Projecto de máquinas de estados microprogramadas com endereçamento

explícito e com endereçamento implícito; Exemplos.

2015/2016

Nuno.Roma@tecnico.ulisboa.pt

# Sistemas Digitais (SD)

#### Máquinas de Estado Microprogramadas: Endereçamento Explícito/Implícito

#### **Aula Anterior**

#### Na aula anterior:

- ▶ Projecto de máquinas de estados microprogramadas:

- Circuito de dados

- Circuito de controlo

- ▶ Implementação com ROMs

- ▶ Exemplos

#### **Planeamento**

| SEMANA          | TEÓRICA 1                                                                          | TEÓRICA 2                                                          | PROBLEMAS/LABORATÓRIO |  |  |  |

|-----------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------|--|--|--|

| 14/Set a 19/Set | Introdução                                                                         | Sistemas de Numeração e Códigos                                    |                       |  |  |  |

| 21/Set a 26/Set | Álgebra de Boole                                                                   | Elementos de Tecnologia                                            | P0                    |  |  |  |

| 28/Set a 3/Out  | Funções Lógicas                                                                    | Minimização de Funções Booleanas (I)                               | LO                    |  |  |  |

| 5/Out a 10/Out  | Minimização de Funções Booleanas (II)                                              | Def. Circuito Combinatório; Análise Temporal                       | P1                    |  |  |  |

| 12/Out a 17/Out | Circuitos Combinatórios (I) – Codif., MUXs, etc.                                   | Circuitos Combinatórios (II) - Som., Comp., etc.                   | L1                    |  |  |  |

| 19/Out a 24/Out | Circuitos Combinatórios (III) - ALUs                                               | Linguagens de Descrição e Simulação de<br>Circuitos Digitais       | P2                    |  |  |  |

| 26/Out a 31/Out | Circuitos Sequenciais: Latches                                                     | Circuitos Sequenciais: Flip-Flops                                  | L2                    |  |  |  |

| 2/Nov a 7/Nov   | Caracterização Temporal                                                            | Registos                                                           | P3                    |  |  |  |

| 9/Nov a 14/Nov  | Revisões Teste 1                                                                   | Contadores                                                         | L3                    |  |  |  |

| 16/Nov a 21/Nov | Síntese de Circuitos Sequenciais: Definições                                       | Síntese de Circuitos Sequenciais: Minimização do número de estados | P4                    |  |  |  |

| 23/Nov a 28/Nov | Síntese de Circuitos Sequenciais: Síntese com Contadores                           | Memórias                                                           | L4                    |  |  |  |

| 30/Nov a 5/Dez  | Máq. Estado Microprogramadas: Circuito de<br>Dados e Circuito de Controlo          | Máq. Estado Microprogramadas:<br>Endereçamento Explícito/Implícito | P5                    |  |  |  |

| 7/Dez a 12/Dez  | Circuitos de Controlo, Transferência e<br>Processamento de Dados de um Processador | Lógica Programável                                                 | L5                    |  |  |  |

| 14/Dez a 18/Dez | P6                                                                                 | P6                                                                 | L6                    |  |  |  |

Prof. Nuno Roma Sistemas Digitais 2015/16

### Sumário

#### ■ Tema da aula de hoje:

- ▶ Projecto de máquinas de estados microprogramadas:

- com endereçamento explícito

- com endereçamento implícito

- ▶ Exemplos

#### ■ Bibliografia:

- M. Mano, C. Kime: Secção 7.13

- G. Arroz, J. Monteiro, A. Oliveira: Secção 7.5

- G. Arroz, C. Sêrro, "Sistemas Digitais: Apontamentos das Aulas Teóricas", IST, 2005: Secções 19.1 a 19.3 (disponível no Fenix)

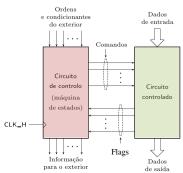

# Circuito de Dados e Circuito de Controlo

#### Circuito de Dados e Circuito de Controlo (Revisão)

- Os sistemas digitais com alguma complexidade tornam-se difíceis de ser projectados como vulgares máquinas sequenciais síncronas, porque:

- Diagramas de estados / tabela de estados de grande dimensão

- Elevado número de:

- o Entradas

- o Saídas

- o Estados.

**Solução:** organizar esses sistemas hierarquicamente, estabelecendo uma divisão clara entre:

- circuito de dados dá suporte ao fluxo e à manipulação de dados;

- circuito de controlo controla o circuito de dados.

Prof. Nuno Roma

Sistemas Digitais 2015/16

5

# Circuito de Dados e Circuito de Controlo

Circuito de Dados e Circuito de Controlo (Revisão)

- ▶ Em geral:

- O circuito de dados (controlado) é formado por um conjunto de módulos simples, tais como contadores, registos, multiplexeres, somadores, comparadores, memórias, algumas portas lógicas, etc, podendo ser combinatório ou sequencial.

- O circuito de controlo é sempre um circuito sequencial síncrono.

Prof. Nuno Roma

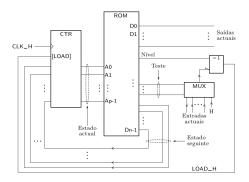

# **Controlo por ROM**

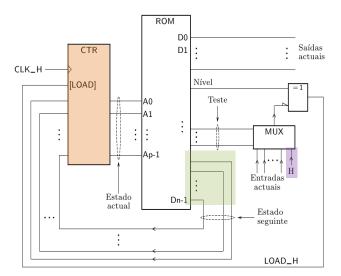

#### ■ Controlo por ROM (Revisão)

- ► A memória **ROM** substitui a lógica combinatória para gerar:

- Estado seguinte

- Saída do circuito

- ► Entradas da ROM (barramento de endereços):

- Entradas externas da máquina de estados

- Estado actual

- ► Saídas da ROM (barramento de dados):

- Saídas para o exterior da máquina de estados

- Saídas (comandos) internas + estado seguinte

Prof. Nuno Roma

Sistemas Digitais 2015/16

7

# **Exemplo**

#### Exemplo (simples)

- ▶ 3 estados:

- A  $(Q_1Q_0=00)$

- B (Q<sub>1</sub>Q<sub>0</sub>=01)

- C  $(Q_1Q_0=10)$

- ▶ 2 entradas: I0 e I1

- 2 saídas: X e Y

- X\_H C Y\_H B H 10\_H L

► Formato da palavra na ROM:

- ▶ Dimensão mínima da ROM:

- 12 endereços de 4 bits

Como reduzir a dimensão da ROM (nº de endereços)?

Prof. Nuno Roma

Sistemas Digitais 2015/16

# CONTROLO POR ROM COM ENDEREÇAMENTO EXPLÍCITO

Prof. Nuno Roma Sistemas Digitais 2015/16

# Controlo por ROM com Endereçamento Explícito

9

Controlo por ROM com Endereçamento Explícito

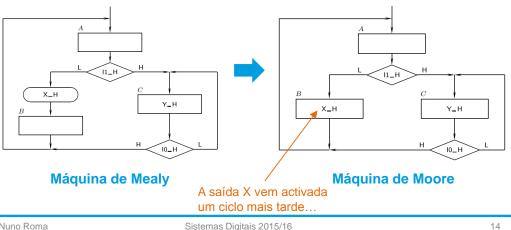

- ▶ Para reduzir o número de endereços, as entradas externas são retiradas do barramento de endereços. Consequências:

- Eliminar o efeito das entradas nas saídas, transformando a máquina de Mealy em máquina de Moore;

- Cada estado actual só pode evoluir para um de dois estados seguintes (incluindo, eventualmente, o próprio).

Prof. Nuno Roma Sistemas Digitais 2015/16 10

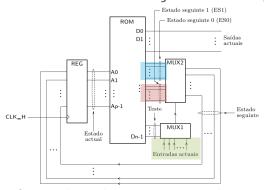

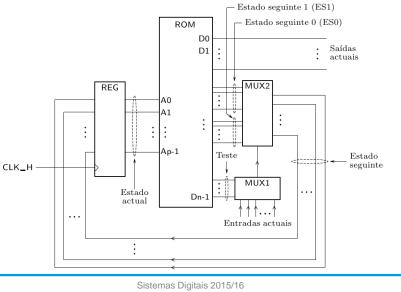

# Controlo por ROM com **Endereçamento Explícito**

■ Controlo por ROM com Endereçamento Explícito

Prof. Nuno Roma

11

# **Controlo por ROM com Endereçamento Explícito**

Controlo por ROM com Endereçamento Explícito

Prof. Nuno Roma

Sistemas Digitais 2015/16

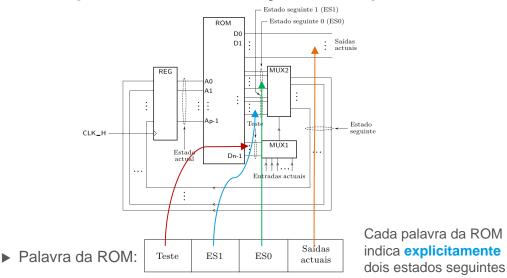

## Controlo por ROM com **Endereçamento Explícito**

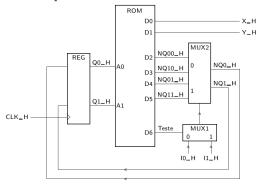

#### Controlo por ROM com Endereçamento Explícito

- ▶ O MUX1 tem as suas entradas ligadas às entradas primárias do circuito de controlo. O campo de teste da ROM permite, para cada estado actual, escolher a entrada ou combinações de entradas a testar.

- Se a entrada seleccionada tiver o valor 0, o estado seguinte escolhido é o que vier indicado no campo ES0;

- No caso contrário, será o estado seguinte ES1.

Prof. Nuno Roma Sistemas Digitais 2015/16 13

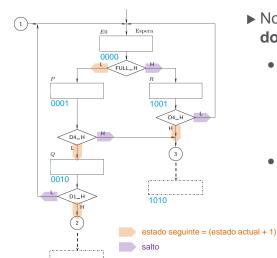

# **Exemplo**

#### Exemplo (simples)

▶ O fluxograma original (máq. Mealy) vai ter de ser transformado, de modo a assumir um comportamento do tipo máquina de **Moore**:

Sistemas Digitais 2015/16 Prof. Nuno Roma

#### Exemplo (simples)

▶ Diagrama de blocos de um controlador implementado com ROM com endereçamento explícito:

▶ Formato de cada palavra da ROM:

Prof. Nuno Roma

Sistemas Digitais 2015/16

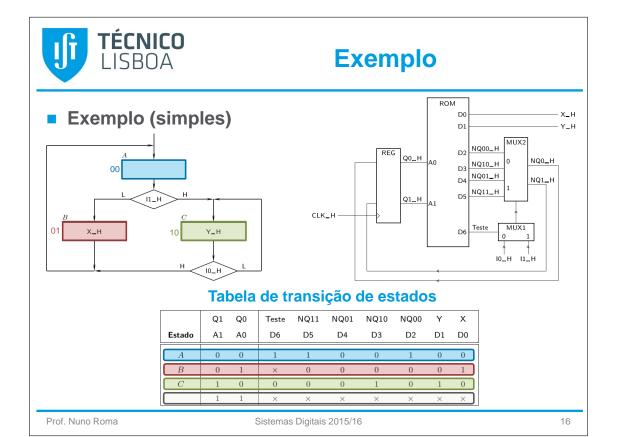

#### Exemplo (simples)

#### Tabela de transição de estados

|        | Q1 | Q0 | Teste | NQ11 | NQ01 | NQ10 | NQ00 | Υ  | Χ  |

|--------|----|----|-------|------|------|------|------|----|----|

| Estado | A1 | Α0 | D6    | D5   | D4   | D3   | D2   | D1 | D0 |

| A      | 0  | 0  | 1     | 1    | 0    | 0    | 1    | 0  | 0  |

| В      | 0  | 1  | ×     | 0    | 0    | 0    | 0    | 0  | 1  |

| C      | 1  | 0  | 0     | 0    | 0    | 1    | 0    | 1  | 0  |

|        | 1  | 1  | ×     | ×    | ×    | ×    | ×    | ×  | ×  |

#### Conteúdo da ROM

| Endereço | Dados   |

|----------|---------|

| 0h       | 1100100 |

| 1h       | 0000001 |

| 2h       | 0001010 |

| 3h       | 0000000 |

- ► Circuito controlador original:

- 12 endereços de 4 bits (48 bits) → Mem. normalizada: 16x4 bits

- ► Circuito controlador com endereçamento explícito da ROM:

- 3 endereços de 7 bits (21 bits) → Mem. normalizada: 4x8 bits

Prof. Nuno Roma

Sistemas Digitais 2015/16

17

# **Exemplo**

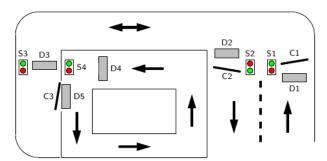

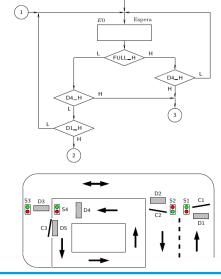

Exemplo: acesso a um parque de estacionamento

- O acesso faz-se por uma via de sentido único, controlada na entrada e na saída pelas <u>cancelas</u> C1 a C3, pelos <u>semáforos</u> S1 a S4, e pelos <u>sensores</u> D1 a D5.

- ▶ O controlador contém um contador ascendente/descendente, que guarda a informação sobre o <u>número de carros estacionados no parque</u>.

Prof. Nuno Roma Sistemas Digitais 2015/16

■ Exemplo: acesso a um parque de estacionamento

- ► Funcionamento:

- A saída é detectada pela presença de um carro que pisa D4. Se não há entrada em curso, o semáforo S4 fica verde e a cancela C3 abre. Em seguida, espera-se que o carro pise D5 e saia, para se fechar a cancela e colocar o semáforo S4 em vermelho. Entretanto, coloca-se o semáforo S2 a verde. Quando o carro pisa D2, abre-se C2, que se mantém aberta enquanto a viatura estiver a pisar D2. Quando o carro deixar de pisar D2, o semáforo S2 passa a vermelho e C2 fecha. Nessa altura desconta-se uma unidade no contador de lugares ocupados no parque.

Prof. Nuno Roma Sistemas Digitais 2015/16 19

# **Exemplo**

■ Exemplo: acesso a um parque de estacionamento

20

- ► Funcionamento:

- A entrada começa com um carro a pisar D1. Se não há saída em curso, o semáforo S1 fica verde e a cancela C1 abre, ficando aberta enquanto o carro é detectado por D1. Quando o carro deixa D1, S3 fica a verde, e quando chega a D3 a cancela C3 é aberta e o carro entra, passando S3 a vermelho e ficando o circuito à espera que D5 seja pisado. Só depois de D5 deixar de ser pisado é que C3 fecha. Nessa altura, o contador é incrementado.

Prof. Nuno Roma Sistemas Digitais 2015/16

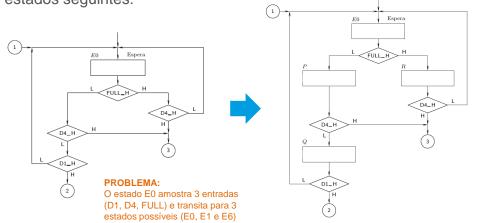

■ Fluxograma do circuito de controlo

Prof. Nuno Roma

Sistemas Digitais 2015/16

21

# **Exemplo**

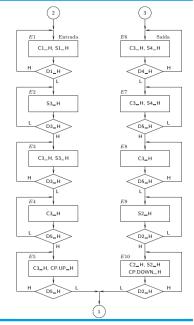

#### Fluxograma do circuito de controlo

▶ É necessário acrescentar alguns estados para garantir que, de qualquer estado actual, apenas se prossegue para um de dois estados seguintes:

Prof. Nuno Roma

Sistemas Digitais 2015/16

Sistemas Digitais 2015/16

Prof. Nuno Roma

# **Exemplo**

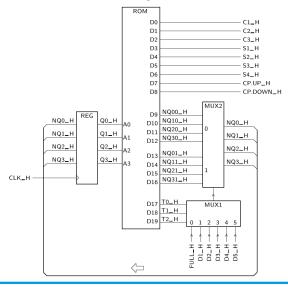

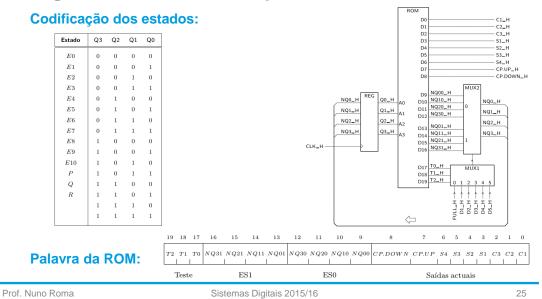

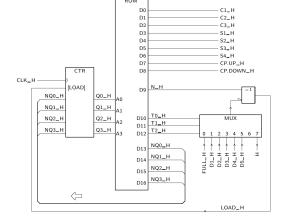

Diagrama de blocos da máquina de estados

Prof. Nuno Roma

Sistemas Digitais 2015/16

24

Diagrama de blocos da máquina de estados

# **Exemplo**

26

Diagrama de blocos da máquina de estados

#### Tabela de Transição de Estados

|        |    |    |    |    |     | Teste |     |      | ES   | 1    |      |      | ES   | 0    |      |         | S     | aídas | acti | ıais |    |    |    |    |

|--------|----|----|----|----|-----|-------|-----|------|------|------|------|------|------|------|------|---------|-------|-------|------|------|----|----|----|----|

|        | Q3 | Q2 | Q1 | Q0 | T2  | Т1    | T0  | NQ31 | NQ21 | NQ11 | NQ01 | NQ30 | NQ20 | NQ10 | NQ00 | CP.DOWN | CP.UP | S4    | S3   | S2   | S1 | С3 | C2 | C1 |

| Estado | A3 | A2 | Α1 | A0 | D19 | D18   | D17 | D16  | D15  | D14  | D13  | D12  | D11  | D10  | D9   | D8      | D7    | D6    | D5   | D4   | D3 | D2 | D1 | D0 |

| E0     | 0  | 0  | 0  | 0  | 0   | 0     | 0   | 1    | 1    | 0    | 1    | 1    | 0    | 1    | 1    | 0       | 0     | 0     | 0    | 0    | 0  | 0  | 0  | 0  |

| E1     | 0  | 0  | 0  | 1  | 0   | 0     | 1   | 0    | 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0       | 0     | 0     | 0    | 0    | 1  | 0  | 0  | 1  |

| E2     | 0  | 0  | 1  | 0  | 0   | 1     | 1   | 0    | 0    | 1    | 1    | 0    | 0    | 1    | 0    | 0       | 0     | 0     | 1    | 0    | 0  | 0  | 0  | 0  |

| E3     | 0  | 0  | 1  | 1  | 0   | 1     | 1   | 0    | 0    | 1    | 1    | 0    | 1    | 0    | 0    | 0       | 0     | 0     | 1    | 0    | 0  | 1  | 0  | 0  |

| E4     | 0  | 1  | 0  | 0  | 1   | 0     | 1   | 0    | 1    | 0    | 1    | 0    | 1    | 0    | 0    | 0       | 0     | 0     | 0    | 0    | 0  | 1  | 0  | 0  |

| E5     | 0  | 1  | 0  | 1  | 1   | 0     | 1   | 0    | 1    | 0    | 1    | 0    | 0    | 0    | 0    | 0       | 1     | 0     | 0    | 0    | 0  | 1  | 0  | 0  |

| E6     | 0  | 1  | 1  | 0  | 1   | 0     | 0   | 0    | 1    | 1    | 0    | 0    | 1    | 1    | 1    | 0       | 0     | 1     | 0    | 0    | 0  | 1  | 0  | 0  |

| E7     | 0  | 1  | 1  | 1  | 1   | 0     | 1   | 1    | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 0       | 0     | 1     | 0    | 0    | 0  | 1  | 0  | 0  |

| E8     | 1  | 0  | 0  | 0  | 1   | 0     | 1   | 1    | 0    | 0    | 0    | 1    | 0    | 0    | 1    | 0       | 0     | 0     | 0    | 0    | 0  | 1  | 0  | 0  |

| E9     | 1  | 0  | 0  | 1  | 0   | 1     | 0   | 1    | 0    | 1    | 0    | 1    | 0    | 0    | 1    | 0       | 0     | 0     | 0    | 1    | 0  | 0  | 0  | 0  |

| E10    | 1  | 0  | 1  | 0  | 0   | 1     | 0   | 1    | 0    | 1    | 0    | 0    | 0    | 0    | 0    | 1       | 0     | 0     | 0    | 1    | 0  | 0  | 1  | 0  |

| P      | 1  | 0  | 1  | 1  | 1   | 0     | 0   | 0    | 1    | 1    | 0    | 1    | 1    | 0    | 0    | 0       | 0     | 0     | 0    | 0    | 0  | 0  | 0  | 0  |

| Q      | 1  | 1  | 0  | 0  | 0   | 0     | 1   | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0       | 0     | 0     | 0    | 0    | 0  | 0  | 0  | 0  |

| R      | 1  | 1  | 0  | 1  | 1   | 0     | 0   | 0    | 1    | 1    | 0    | 0    | 0    | 0    | 0    | 0       | 0     | 0     | 0    | 0    | 0  | 0  | 0  | 0  |

| _      | 1  | 1  | 1  | 0  | ×   | ×     | ×   | ×    | ×    | ×    | ×    | ×    | ×    | ×    | ×    | ×       | ×     | ×     | ×    | ×    | ×  | ×  | ×  | ×  |

| _      | 1  | 1  | 1  | 1  | ×   | ×     | ×   | ×    | ×    | ×    | ×    | ×    | ×    | ×    | ×    | ×       | ×     | ×     | ×    | ×    | ×  | ×  | ×  | ×  |

Dimensão da ROM: 16 endereços de 20 bits (320 bits)

Prof. Nuno Roma Sistemas Digitais 2015/16

# CONTROLO POR ROM COM ENDEREÇAMENTO IMPLÍCITO

Prof. Nuno Roma Sistemas Digitais 2015/16 27

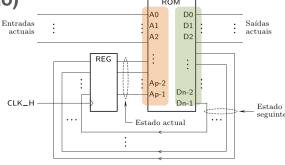

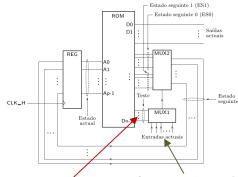

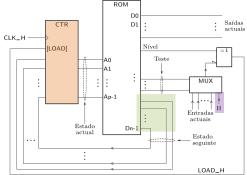

# Controlo por ROM com Endereçamento Implícito

#### ■ Controlo por ROM com Endereçamento Implícito

# ROM DO DI Estado seguinte 0 (ESO) Saídas actuais AP-1 Teste Estado seguinte 0 (ESO) MUX2 AP-1 Teste Estado seguinte 0 (ESO)

**Endereçamento Explícito**

#### Endereçamento Implícito

- Para reduzir as dimensões da ROM, um dos endereços de estado seguinte está implícito: Estado Seguinte = Estado Actual + 1

- O registo é substituído por um contador com carregamento paralelo.

Prof. Nuno Roma Sistemas Digitais 2015/16 28

# Controlo por ROM com Endereçamento Implícito

#### Controlo por ROM com Endereçamento Implícito

#### Alterações:

- O registo é substituído por um contador com carregamento paralelo.

- O fluxograma é ajustado de modo a garantir que cada estado evolui para:

- Estado seguinte da contagem: EstadoSeguinte=EstadoActual+1

ou

Saltar para um outro estado qualquer, n\u00e3o imediatamente a seguir em termos de contagem

Não é necessário ter dois campos de estado seguinte (ES0 e ES1) na ROM

Palavras mais curtas

Prof. Nuno Roma

Sistemas Digitais 2015/16

29

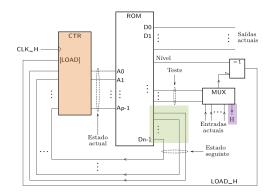

# Controlo por ROM com Endereçamento Implícito

#### ■ Controlo por ROM com Endereçamento Implícito

Prof. Nuno Roma

Sistemas Digitais 2015/16

# Controlo por ROM com Endereçamento Implícito

#### Controlo por ROM com Endereçamento Implícito

- ▶ Modos de contagem:

- [INC] O estado seguinte corresponde ao valor seguinte da contagem:

#### Estado Seguinte = Estado Actual + 1

**[LOAD]** - O estado seguinte corresponde a um estado que não corresponde ao estado seguinte de <u>contagem</u>:

#### Estado Seguinte = Outro Estado (salto)

- o Salto condicional depende do valor de uma variável de entrada:

- campo Teste selecciona a variável de entrada;

- campo Nível decide se o salto se deve efectuar quando ela tiver o valor 1 ou o valor 0;

- Salto incondicional:

- Selecção da entrada H do MUX (sempre activa);

- campo Nível a 1.

Prof. Nuno Roma

Sistemas Digitais 2015/16

31

# **Exemplo**

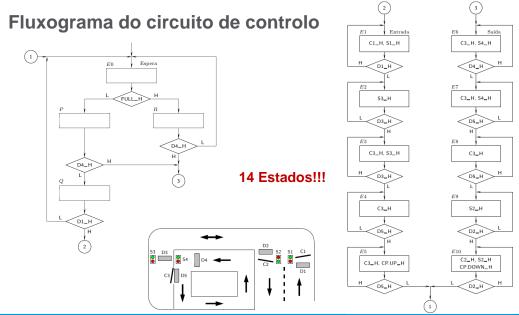

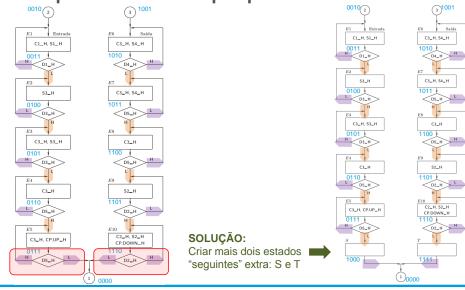

Exemplo: acesso a um parque de estacionamento

- Novos cuidados a ter na codificação dos estados:

- Sempre que possível: é necessário garantir que o estado seguinte a cada estado corresponde à codificação dada por:

estado seguinte = (estado actual + 1);

<u>Caso não seja possível</u>: codificar com um salto

Prof. Nuno Roma

Sistemas Digitais 2015/16

■ Exemplo: acesso a um parque de estacionamento

#### **PROBLEMA:**

Os estados E5 e E10 transitam sempre através de um salto!!!

Prof. Nuno Roma

Sistemas Digitais 2015/16

33

# **Exemplo**

■ Exemplo: acesso a um parque de estacionamento

Prof. Nuno Roma

Sistemas Digitais 2015/16

Exemplo: acesso a um parque de estacionamento

Prof. Nuno Roma

Sistemas Digitais 2015/16

35

# **Exemplo**

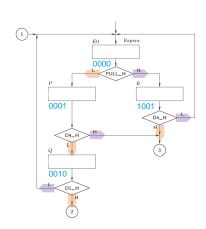

■ Exemplo: acesso a um parque de estacionamento

Diagrama de blocos:

Palavra da ROM:

NNQ3 NQ2 NQ1 NQ0 T2T1T0CP.DOWN CP.UP S4 S3 S2 S1 C3 C2 C1 Saídas actuais

Prof. Nuno Roma

Sistemas Digitais 2015/16

#### Diagrama de blocos da máquina de estados

Tabela de Transição de Estados

|        | rabola do Transigao do |    |    |    |     |     |     |             |     |     |                |    |         |       |    |    |    |    |    |    |    |

|--------|------------------------|----|----|----|-----|-----|-----|-------------|-----|-----|----------------|----|---------|-------|----|----|----|----|----|----|----|

|        |                        |    |    |    | ES  |     |     | Teste Nível |     |     | Saídas actuais |    |         |       |    |    |    |    |    |    |    |

|        | Q3                     | Q2 | Q1 | Q0 | NQ3 | NQ2 | NQ1 | NQ0         | T2  | Т1  | T0             | N  | CP.DOWN | CP.UP | S4 | S3 | S2 | S1 | С3 | C2 | C1 |

| Estado | А3                     | A2 | Α1 | A0 | D16 | D15 | D14 | D13         | D12 | D11 | D10            | D9 | D8      | D7    | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| E0     | 0                      | 0  | 0  | 0  | 1   | 0   | 0   | 1           | 0   | 0   | 0              | 1  | 0       | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| P      | 0                      | 0  | 0  | 1  | 1   | 0   | 1   | 0           | 1   | 0   | 0              | 1  | 0       | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Q      | 0                      | 0  | 1  | 0  | 0   | 0   | 0   | 0           | 0   | 0   | 1              | 0  | 0       | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| E1     | 0                      | 0  | 1  | 1  | 0   | 0   | 1   | 1           | 0   | 0   | 1              | 1  | 0       | 0     | 0  | 1  | 0  | 1  | 1  | 0  | 1  |

| E2     | 0                      | 1  | 0  | 0  | 0   | 1   | 0   | 0           | 0   | 1   | 1              | 0  | 0       | 0     | 0  | 1  | 0  | 0  | 1  | 0  | 0  |

| E3     | 0                      | 1  | 0  | 1  | 0   | 1   | 0   | 1           | 0   | 1   | 1              | 1  | 0       | 0     | 0  | 1  | 0  | 0  | 1  | 0  | 0  |

| E4     | 0                      | 1  | 1  | 0  | 0   | 1   | 1   | 0           | 1   | 0   | 1              | 0  | 0       | 0     | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| E5     | 0                      | 1  | 1  | 1  | 0   | 1   | 1   | 1           | 1   | 0   | 1              | 1  | 0       | 1     | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| S      | 1                      | 0  | 0  | 0  | 0   | 0   | 0   | 0           | 1   | 1   | 1              | 1  | 0       | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| R      | 1                      | 0  | 0  | 1  | 0   | 0   | 0   | 0           | 1   | 0   | 0              | 0  | 0       | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| E6     | 1                      | 0  | 1  | 0  | 1   | 0   | 1   | 0           | 1   | 0   | 0              | 1  | 0       | 0     | 1  | 0  | 0  | 0  | 1  | 0  | 0  |

| E7     | 1                      | 0  | 1  | 1  | 1   | 0   | 1   | 1           | 1   | 0   | 1              | 1  | 0       | 0     | 1  | 0  | 0  | 0  | 1  | 0  | 0  |

| E8     | 1                      | 1  | 0  | 0  | 1   | 1   | 0   | 0           | 1   | 0   | 1              | 1  | 0       | 0     | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| E9     | 1                      | 1  | 0  | 1  | 1   | 1   | 0   | 1           | 0   | 1   | 0              | 0  | 0       | 0     | 0  | 0  | 1  | 0  | 0  | 0  | 0  |

| E10    | 1                      | 1  | 1  | 0  | 1   | 1   | 1   | 0           | 0   | 1   | 0              | 1  | 1       | 0     | 0  | 0  | 1  | 0  | 0  | 1  | 0  |

| T      | 1                      | 1  | 1  | 1  | 0   | 0   | 0   | 0           | 1   | 1   | 1              | 1  | 0       | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

Dimensão da ROM: 16 endereços de 17 bits (272 bits)

Prof. Nuno Roma Sistemas Digitais 2015/16 37

#### Próxima Aula

#### Tema da Próxima Aula:

- ▶ Circuitos de Controlo, Transferência e Processamento de Dados

- ▶ Exemplo de uma arquitectura simples de um processador

Prof. Nuno Roma

Sistemas Digitais 2015/16

#### Agradecimentos

Algumas páginas desta apresentação resultam da compilação de várias contribuições produzidas por:

- Guilherme Arroz

- Horácio Neto

- Nuno Horta

- Pedro Tomás

Prof. Nuno Roma

Sistemas Digitais 2015/16