# SISTEMAS DIGITAIS (SD)

#### **MEEC**

#### Acetatos das Aulas Teóricas

Versão 4.0 - Português

#### Aula Nº 09:

Título: Circuitos combinatórios: descodificadores, codificadores, multiplexers e de-

multiplexers

Sumário: Descodificadores, codificadores, multiplexers e demultiplexers

2015/2016

Nuno.Roma@tecnico.ulisboa.pt

# Sistemas Digitais (SD)

Circuitos combinatórios: descodificadores, codificadores, multiplexers e demultiplexers

### **Aula Anterior**

#### Na aula anterior:

- ▶ Noção de circuito combinatório;

- ▶ Tempo de propagação num circuito;

- ▶ Dispositivos lógicos especiais:

- Buffer de três estados (tri-state);

- Portas de passagem (transmission gates).

## **Planeamento**

| SEMANA          | TEÓRICA 1                                                                          | TEÓRICA 2                                                                     | PROBLEMAS/LABORATÓRIO |

|-----------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------|

| 14/Set a 19/Set | Introdução                                                                         | Sistemas de Numeração e Códigos                                               |                       |

| 21/Set a 26/Set | Álgebra de Boole                                                                   | Elementos de Tecnologia                                                       | P0                    |

| 28/Set a 3/Out  | Funções Lógicas                                                                    | Minimização de Funções Booleanas (I)                                          | LO                    |

| 5/Out a 10/Out  | Minimização de Funções Booleanas (II)                                              | Def. Circuito Combinatório; Análise Temporal                                  | P1                    |

| 12/Out a 17/Out | Circuitos Combinatórios (I) – Codif., MUXs, etc.                                   | Circuitos Combinatórios (II) – Som., Comp., etc.                              | L1                    |

| 19/Out a 24/Out | Circuitos Combinatórios (III) - ALUs                                               | Circuitos Sequenciais: Latches                                                | P2                    |

| 26/Out a 31/Out | Circuitos Sequenciais: Flip-Flops                                                  | Ling. de Descrição e Simulação de HW (ferramentas disponíveis no laboratório) | L2                    |

| 2/Nov a 7/Nov   | Caracterização Temporal                                                            | Registos                                                                      | P3                    |

| 9/Nov a 14/Nov  | Revisões Teste 1                                                                   | Contadores                                                                    | L3                    |

| 16/Nov a 21/Nov | Síntese de Circuitos Sequenciais: Definições                                       | Síntese de Circuitos Sequenciais: Minimização do número de estados            | P4                    |

| 23/Nov a 28/Nov | Síntese de Circuitos Sequenciais: Síntese com Contadores                           | Memórias                                                                      | L4                    |

| 30/Nov a 5/Dez  | Máq. Estado Microprogramadas: Circuito de<br>Dados e Circuito de Controlo          | Máq. Estado Microprogramadas:<br>Endereçamento Explícito/Implícito            | P5                    |

| 7/Dez a 12/Dez  | Circuitos de Controlo, Transferência e<br>Processamento de Dados de um Processador | Lógica Programável                                                            | L5                    |

| 14/Dez a 18/Dez | P6                                                                                 | P6                                                                            | L6                    |

Prof. Nuno Roma Sistemas Digitais 2015/16

## **Sumário**

### ■ Tema da aula de hoje:

- ► Circuitos combinatórios típicos:

- Descodificadores

- Codificadores

- Multiplexers

- Demultiplexers

### Bibliografia:

- M. Mano, C. Kime: Secções 3.7 a 3.9

- G. Arroz, J. Monteiro, A. Oliveira: Secções 4.2 a 4.5

#### **Descodificador**

#### Descodificador (em inglês, Decoder)

▶ O descodificador binário é um circuito combinatório que permite, perante uma combinação de entradas, activar uma e só uma saída.

|   |   | O0    |   |   |   |

|---|---|-------|---|---|---|

| 0 | 0 | 1 0 0 | 0 | 0 | 0 |

| 0 | 1 | 0     | 1 | 0 | 0 |

| 1 | 0 | 0     | 0 | 1 | 0 |

| 1 | 1 | 0     | 0 | 0 | 1 |

No símbolo do componente, o índice dos sinais de entrada/saída permite identificar claramente as saídas e o "peso" de cada um dos sinais de entrada.

Prof. Nuno Roma

Sistemas Digitais 2015/16

5

#### **Descodificador**

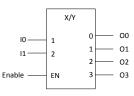

#### ■ Descodificador com entrada de activação (*Enable*):

▶ A entrada de **ENABLE** permite, quando activa (neste caso, a "1"), que o descodificador funcione normalmente. Quando não activa, inibe o seu funcionamento fazendo com que todas as saídas fiquem inactivas (neste caso, todas a "0").

| EN | I1 | Ι0 | O0 | O1 | O2 | О3 |

|----|----|----|----|----|----|----|

| 1  | 0  | 0  | 1  | 0  | 0  | 0  |

| 1  | 0  | 1  | 0  | 1  | 0  | 0  |

| 1  | 1  | 0  | 0  | 0  | 1  | 0  |

| 1  | 1  | 1  | 0  | 0  | 0  | 1  |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0  | 0  | 1  | 0  | 0  | 0  | 0  |

| 0  | 1  | 0  | 0  | 0  | 0  | 0  |

| 0  | 1  | 1  | 0  | 0  | 0  | 0  |

#### **DESCODIFICADOR 2:4**

Prof. Nuno Roma

Sistemas Digitais 2015/16

### **Descodificador**

#### Descodificador: estrutura interna

- ▶ A figura representa a estrutura interna de um descodificador binário de 2 entradas.

- ► Cada saída representa uma das combinações possíveis das entradas

|   | I1 | 10 |   |   |                  |   |

|---|----|----|---|---|------------------|---|

| Ī | 0  | 0  | 1 | 0 | 0                | 0 |

|   | 0  | 1  | 0 | 1 | 0                | 0 |

|   | 1  | 0  | 0 | 0 | 0<br>0<br>1<br>0 | 0 |

|   | 1  | 1  | 0 | 0 | 0                | 1 |

$$O_0 = \overline{I_1} . \overline{I_0}$$

$O_2 = I_1 . \overline{I_0}$

$$O_2 = I_1 \cdot \overline{I_0}$$

$$O_1 = \overline{I_1} \cdot I_0$$

$$O_1 = \overline{I_1} \cdot I_0$$

$O_3 = I_1 \cdot I_0$

Prof. Nuno Roma

Sistemas Digitais 2015/16

### **Descodificador**

#### Descodificador com saídas activas a zero

▶ No símbolo do componente, o ∆ na saída indica que esta é activa a "0", i.e., a saída seleccionada tem um "0" e as outras têm um "1". (funciona como se tivesse um inversor na saída)

| I1 | IO | O0 | O1 | O2 | O3 |

|----|----|----|----|----|----|

| 0  | 0  | 0  | 1  | 1  | 1  |

| 0  | 1  | 1  | 0  | 1  | 1  |

| 1  | 0  | 1  | 1  | 0  | 1  |

| 1  | 1  | 1  | 1  | 1  | 0  |

Prof. Nuno Roma

Sistemas Digitais 2015/16

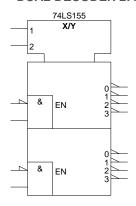

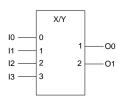

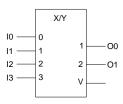

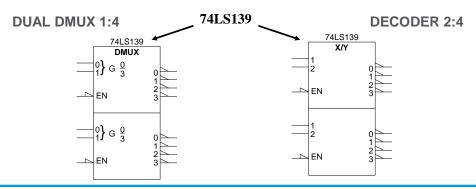

## **Descodificador**

#### ■ Descodificadores: exemplos de componentes

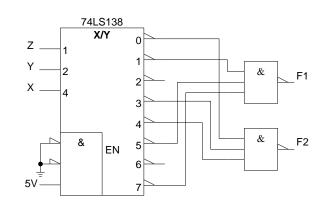

#### **DESCODIFICADOR 3:8**

#### **DUAL DECODER 2:4**

#### **DUAL DECODER 2:4**

Nos 3 exemplos os sinais de saída são activos a zero.

No 138 o Enable é um AND de 3 entradas, 2 delas negadas. No 139 o Enable é activo a zero. No 155 o Enable é um AND de 2 entradas, 1 delas negada.

Prof. Nuno Roma

Sistemas Digitais 2015/16

9

#### **Codificador**

### Codificador (em inglês, encoder):

▶ O codificador binário é um circuito combinatório que indica qual das entradas possíveis é que está activa (neste caso, a "1").

| I3 | I2 | I1 | 10 | O1 | 00 |

|----|----|----|----|----|----|

| 0  | 0  | 0  | 1  | 0  | 0  |

| 0  | 0  | 1  | 0  | 0  | 1  |

| 0  | 1  | 0  | 0  | 1  | 0  |

| 1  | 0  | 0  | 0  | 1  | 1  |

- Nesta versão simples, o codificador só considera 4 das 16 combinações possíveis de entrada.

- ▶ O circuito não distingue a situação de todas as entradas estarem a "0".

- ➤ O circuito não distingue as situações em que estão a "1" mais do que uma entrada.

Prof. Nuno Roma

Sistemas Digitais 2015/16

## **Codificador**

#### Codificador de prioridade:

▶ As entradas deste codificador têm uma ordem de prioridades: em caso de mais de uma entrada activa (a "1") é considerada a de maior prioridade.

| I3 | I2 | I1 | 10 | O1 | O0 | V |

|----|----|----|----|----|----|---|

| 0  | 0  | 0  | 0  | 0  | 0  | 0 |

| 0  | 0  | 0  | 1  | 0  | 0  | 1 |

| 0  | 0  | 1  | X  | 0  | 1  | 1 |

| 0  | 1  | X  | X  | 1  | 0  | 1 |

| 1  | X  | X  | X  | 1  | 1  | 1 |

- ▶ A entrada I3 é a de maior prioridade, seguida da I2, da I1, e a I0 é a de menor prioridade.

- ▶ A saída V suplementar indica se existe pelo menos uma entrada activa (a "1").

Prof. Nuno Roma

Sistemas Digitais 2015/16

11

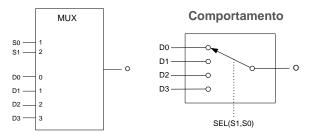

## **Multiplexer**

#### Multiplexer:

➤ O multiplexer é um circuito combinatório que permite, através da especificação dos sinais de selecção, encaminhar uma das N entradas de dados para a saída.

Exemplo: multiplexer 4:1

| S1 | S0 | О  |

|----|----|----|

| 0  | 0  | D0 |

| 0  | 1  | D1 |

| 1  | 0  | D2 |

| 1  | 1  | D3 |

► As entradas de selecção determinam a entrada de dados cujo valor é colocado na saída.

Prof. Nuno Roma

Sistemas Digitais 2015/16

# Multiplexer

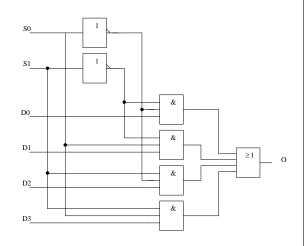

## ■ Multiplexer: estrutura interna

| S1 | S0 | О  |

|----|----|----|

| 0  | 0  | D0 |

| 0  | 1  | D1 |

| 1  | 0  | D2 |

| 1  | 1  | D3 |

$$O = D_0 . \overline{S_1} . \overline{S_0} + D_1 . \overline{S_1} . S_0 + D_2 . S_1 . \overline{S_0} + D_3 . S_1 . S_0$$

Prof. Nuno Roma

Sistemas Digitais 2015/16

13

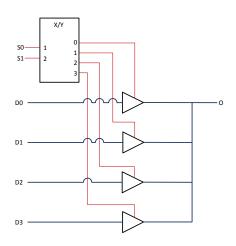

## **Multiplexer**

## ■ Multiplexer: estrutura interna alternativa

| <b>S</b> 1 | S0 | О  |

|------------|----|----|

| 0          | 0  | D0 |

| 0          | 1  | D1 |

| 1          | 0  | D2 |

| 1          | 1  | D3 |

Prof. Nuno Roma

Sistemas Digitais 2015/16

## **Multiplexer**

## Multiplexer: simbologia

MULTIPLEXER 4:1 simples

## MULTIPLEXER 4:1 com enable

| EN | <b>S</b> 1 | S0 | О  |

|----|------------|----|----|

| 1  | 0          | 0  | D0 |

| 1  | 0          | 1  | D1 |

| 1  | 1          | 0  | D2 |

| 1  | 1          | 1  | D3 |

| 0  | X          | X  | 0  |

Prof. Nuno Roma

Sistemas Digitais 2015/16

15

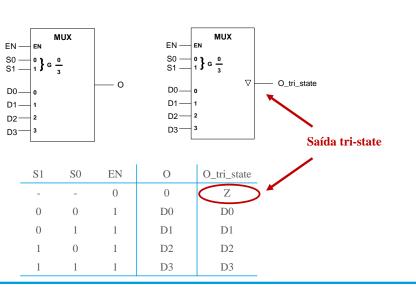

## **Multiplexer**

## Multiplexer: saída tri-state

Prof. Nuno Roma

Sistemas Digitais 2015/16

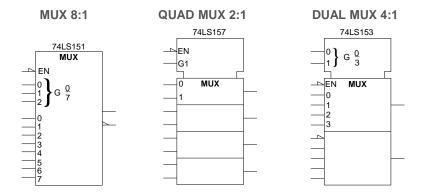

## **Multiplexer**

#### Multiplexers: exemplos de componentes

Nos 3 exemplos os sinais de Enable são activos a zero (a activação do funcionamento normal do componente acontece quando EN=0).

O 74151 tem uma saída suplementar que é a negação da outra.

Prof. Nuno Roma Sistemas Digitais 2015/16 17

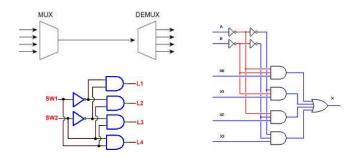

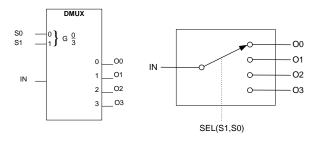

## **Demultiplexer**

#### Demultiplexer:

➤ O demultiplexer é um circuito combinatório que permite, através da especificação dos sinais de selecção, encaminhar a entrada para uma das N saídas.

Exemplo: Demultiplexer 1:4

| <b>S</b> 1 |   |    | 01      |    |    |

|------------|---|----|---------|----|----|

| 0          | 0 | IN | 0<br>IN | 0  | 0  |

| 0          | 1 | 0  | IN      | 0  | 0  |

| 1          | 0 | 0  | 0       | IN | 0  |

| 1          | 1 | 0  | 0       | 0  | IN |

Prof. Nuno Roma

Sistemas Digitais 2015/16

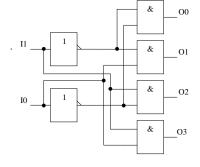

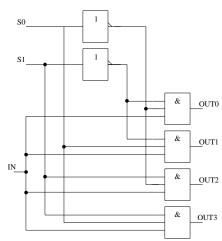

## **Demultiplexer**

#### ■ Demultiplexer: estrutura interna

#### **DEMULTIPLEXER 1:4**

| <b>S</b> 1 | S0 | O0 | O1 | O2 | O3 |

|------------|----|----|----|----|----|

| 0          | 0  | IN | 0  | 0  | 0  |

| 0          | 1  | 0  | IN | 0  | 0  |

| 1          | 0  | 0  | 0  | IN | 0  |

| 1          | 1  | 0  | 0  | 0  | IN |

$$O_0 = IN.\overline{S_1}.\overline{S_0}$$

$O_2 = IN.S_1.\overline{S_0}$

$$O_2 = IN.S_1.\overline{S_0}$$

$$O_1 = IN.\overline{S_1}.S_0$$

$O_3 = IN.S_1.S_0$

$$O_3 = IN.S_1.S_0$$

Prof. Nuno Roma

Sistemas Digitais 2015/16

19

20

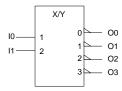

## **Demultiplexer vs Descodificador**

#### Demultiplexeres e Descodificadores:

▶ Um descodificador com enable é equivalente a um demultiplexer, sendo as entradas de dados do primeiro as entradas de selecção do segundo e a entrada de enable do primeiro a entrada de dados do segundo.

Nota: os 2 símbolos abaixo referem a mesma funcionalidade do circuito.

Prof. Nuno Roma Sistemas Digitais 2015/16

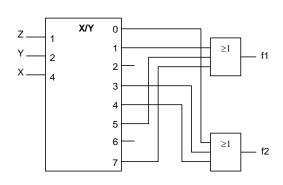

### Descodificadores: aplicações (f. combinatórias)

▶ Realização de funções combinatórias de 3 variáveis com decoders 3:8

$$f1(X,Y,Z) = \sum m(1,5,7)$$

$$f2(X,Y,Z) = \sum m(0,3,4)$$

Prof. Nuno Roma

Sistemas Digitais 2015/16

21

# **Aplicações**

### Descodificadores: aplicações (f. combinatórias)

▶ Realização de funções combinatórias de 3 variáveis com decoders 3:8 com saídas activas a 0.

$$f1(X,Y,Z) = \sum m(1,5,7)$$

$$f2(X,Y,Z) = \sum m(0,3,4)$$

Prof. Nuno Roma

Sistemas Digitais 2015/16

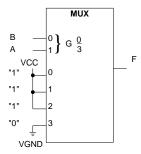

### Multiplexers: aplicações (f. combinatórias)

► Exemplo de realização de funções combinatórias de 2 variáveis com MUX 4:1

$$F = \overline{A} + A\overline{B}$$

| A | В | F |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Prof. Nuno Roma Sistemas Digitais 2015/16

# **Aplicações**

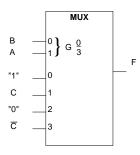

### Multiplexers: aplicações (f. combinatórias)

► Exemplo de realização de funções combinatórias de 3 variáveis com MUX 4:1

$$F = \overline{A} \overline{B} + \overline{A} C + AB\overline{C}$$

| Α | В | С | F |                    |

|---|---|---|---|--------------------|

| 0 | 0 | 0 | 1 |                    |

| 0 | 0 | 1 | 1 | F = 1              |

| 0 | 1 | 0 | 0 |                    |

| 0 | 1 | 1 | 1 | F = C              |

| 1 | 0 | 0 | 0 |                    |

| 1 | 0 | 1 | 0 | F = 0              |

| 1 | 1 | 0 | 1 | $F = \overline{C}$ |

| 1 | 1 | 1 | 0 | r – C              |

Prof. Nuno Roma

Sistemas Digitais 2015/16

24

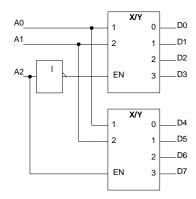

- Descodificadores: aplicações (descodificação)

- ► Exemplo de realização de um DECODER 3:8 tendo por base 2 DECODERs 2:4

Prof. Nuno Roma Sistemas Digitais 2015/16 25

## **Aplicações**

26

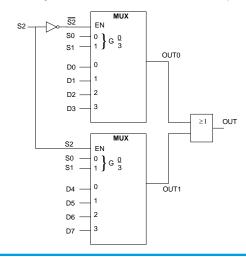

- Multiplexers: aplicações (multiplexagem)

- ▶ Exemplo de realização de um MUX 8:1 tendo por base 2 MUXs 4:1

Prof. Nuno Roma Sistemas Digitais 2015/16

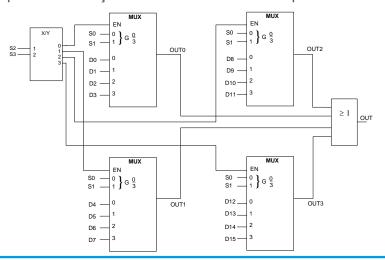

- Multiplexers: aplicações (multiplexagem)

- ▶ Exemplo de realização de um MUX 16:1 tendo por base 4 MUXs 4:1

Prof. Nuno Roma Sistemas Digitais 2015/16

## **Aplicações**

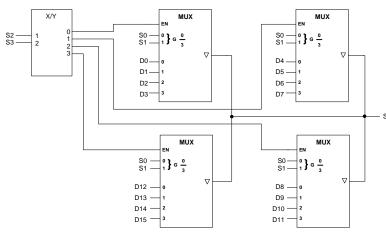

- Multiplexers: aplicações (multiplexagem)

- ► Exemplo de realização de um MUX 16:1 tendo por base 4 MUXs 4:1 tri-state

Prof. Nuno Roma

Sistemas Digitais 2015/16

28

## **Próxima Aula**

Prof. Nuno Roma Sistemas Digitais 2015/16 29

## **Próxima Aula**

#### ■ Tema da Próxima Aula:

- ► Circuitos combinatórios típicos:

- Somadores / Subtractores

- Comparadores

Prof. Nuno Roma

Sistemas Digitais 2015/16

## Agradecimentos

Algumas páginas desta apresentação resultam da compilação de várias contribuições produzidas por:

- Guilherme Arroz

- Horácio Neto

- Nuno Horta

- Pedro Tomás

Prof. Nuno Roma

Sistemas Digitais 2015/16