# SISTEMAS DIGITAIS (SD)

#### **MEEC**

#### Acetatos das Aulas Teóricas

Versão 4.0 - Português

#### Aula Nº 08:

**Título:** Definição de Circuito Combinatório; Tempo de Propagação de um Circuito

Sumário: Noção de circuito combinatório; Tempo de propagação num circuito; Dispos-

itivos lógicos especiais: buffer de três estados (tri-state) e portas de passagem

(transmission gates).

2015/2016

Nuno.Roma@tecnico.ulisboa.pt

## Sistemas Digitais (SD)

Definição de Circuito Combinatório Tempo de Propagação de um Circuito

#### **Aula Anterior**

#### Na aula anterior:

- ▶ Minimização de Karnaugh:

- Agrupamentos de uns e zeros:

- Eixos de simetria;

- o Implicantes e implicados;

- o Implicantes e implicados primos;

- o Implicantes e implicados primos essenciais.

- Método de minimização de Karnaugh:

- o Algoritmo de minimização;

- o Forma normal/mínima disjuntiva;

- o Forma normal/mínima conjuntiva;

- o Funções incompletamente especificadas.

#### **Planeamento**

| SEMANA          | TEÓRICA 1                                                                          | TEÓRICA 2                                                                     | PROBLEMAS/LABORATÓRIO |

|-----------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------|

| 14/Set a 19/Set | Introdução                                                                         | Sistemas de Numeração e Códigos                                               |                       |

| 21/Set a 26/Set | Álgebra de Boole                                                                   | Elementos de Tecnologia                                                       | P0                    |

| 28/Set a 3/Out  | Funções Lógicas                                                                    | Minimização de Funções Booleanas (I)                                          | LO                    |

| 5/Out a 10/Out  | Minimização de Funções Booleanas (II)                                              | Def. Circuito Combinatório; Análise Temporal                                  | P1                    |

| 12/Out a 17/Out | Circuitos Combinatórios (I) – Codif., MUXs, etc.                                   | Circuitos Combinatórios (II) – Som., Comp., etc.                              | L1                    |

| 19/Out a 24/Out | Circuitos Combinatórios (III) - ALUs                                               | Circuitos Sequenciais: Latches                                                | P2                    |

| 26/Out a 31/Out | Circuitos Sequenciais: Flip-Flops                                                  | Ling. de Descrição e Simulação de HW (ferramentas disponíveis no laboratório) | L2                    |

| 2/Nov a 7/Nov   | Caracterização Temporal                                                            | Registos                                                                      | P3                    |

| 9/Nov a 14/Nov  | Revisões Teste 1                                                                   | Contadores                                                                    | L3                    |

| 16/Nov a 21/Nov | Síntese de Circuitos Sequenciais: Definições                                       | Síntese de Circuitos Sequenciais: Minimização do número de estados            | P4                    |

| 23/Nov a 28/Nov | Síntese de Circuitos Sequenciais: Síntese com Contadores                           | Memórias                                                                      | L4                    |

| 30/Nov a 5/Dez  | Máq. Estado Microprogramadas: Circuito de<br>Dados e Circuito de Controlo          | Máq. Estado Microprogramadas:<br>Endereçamento Explícito/Implícito            | P5                    |

| 7/Dez a 12/Dez  | Circuitos de Controlo, Transferência e<br>Processamento de Dados de um Processador | Lógica Programável                                                            | L5                    |

| 14/Dez a 18/Dez | P6                                                                                 | P6                                                                            | L6                    |

Prof. Nuno Roma Sistemas Digitais 2015/16

## Sumário

#### ■ Tema da aula de hoje:

- ▶ Noção de circuito combinatório;

- ▶ Tempo de propagação num circuito;

- ▶ Dispositivos lógicos especiais:

- Buffer de três estados (tri-state);

- Portas de passagem (transmission gates).

#### ■ Bibliografia:

- M. Mano, C. Kime: Secções 3.1.4, 3.4 e 3.1.6

- G. Arroz, J. Monteiro, A. Oliveira: Secção 6.2 e 2.10

## **NOÇÃO DE CIRCUITO COMBINATÓRIO**

Prof. Nuno Roma

Sistemas Digitais 2015/16

5

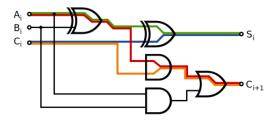

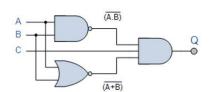

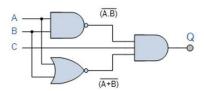

## Noção de Circuito Combinatório

#### Circuito Combinatório:

- ▶ A saída é uma função que depende <u>apenas</u> da entrada actual;

- ► Definido através de:

- Função Booleana Ex:  $Q = (\overline{A.B}).(\overline{A+B}).C$

- Diagrama lógico

- Tabela de verdade

| С | В | Α | Q |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

Prof. Nuno Roma

Sistemas Digitais 2015/16

## Noção de Circuito Combinatório

#### Circuito Combinatório:

▶ A saída é uma função que depende **apenas** da entrada actual;

▶ Definido em contraste com a noção de circuito sequencial, em que a saída depende não só da entrada actual, mas também do valores anteriores dessa entrada...

i.e., circuitos sequenciais têm "efeito de memória", enquanto que um circuito combinatório não.

Veremos daqui a algumas semanas...

Prof. Nuno Roma

Sistemas Digitais 2015/16

7

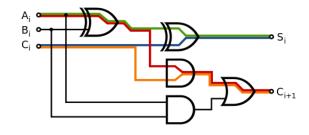

## Noção de Circuito Combinatório

#### Circuito Combinatório:

- ▶ Até ao momento, tem-se assumido um modelo **ideal** dos circuitos lógicos, em que a saída muda *instantaneamente* face aos valores na entrada do circuito.

- Na realidade, todos os circuitos caracterizam-se por um certo tempo de propagação, entre as entradas e as saídas, e que depende no número e complexidade das portas lógicas envolvidas:

Prof. Nuno Roma

Sistemas Digitais 2015/16

## Tempo de Propagação num Circuito Lógico

Prof. Nuno Roma

Sistemas Digitais 2015/16

a

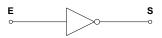

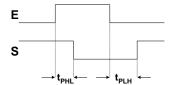

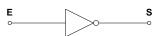

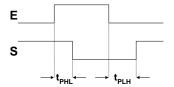

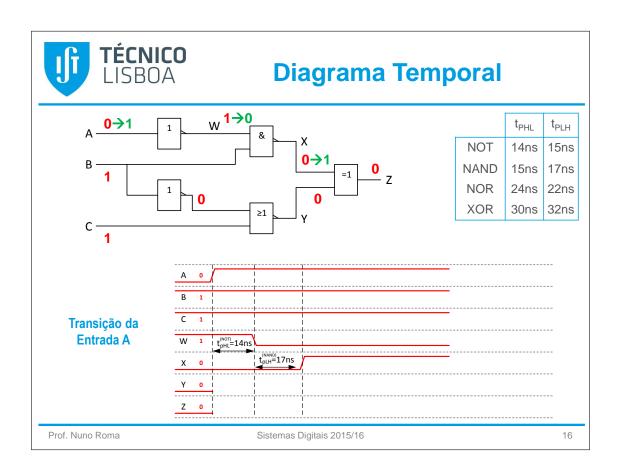

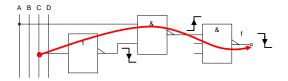

## Tempos de Propagação

- Tempo de Propagação:

- corresponde ao intervalo de tempo necessário para que uma alteração na entrada se propague até à saída de uma determinada porta lógica ou circuito combinatório.

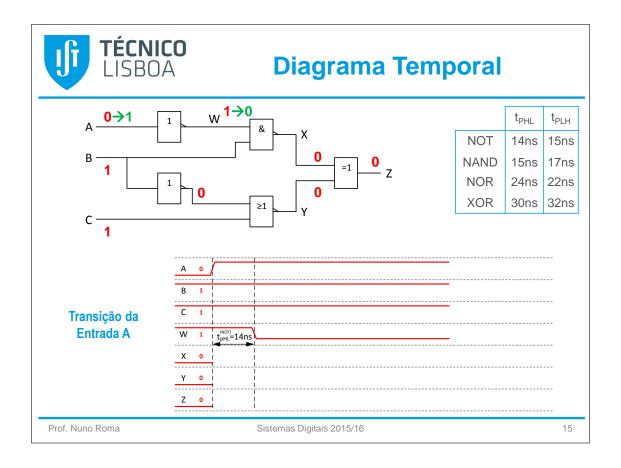

- ▶ t<sub>PHL</sub> Tempo de propagação de H para L na saída, desde a variação da entrada.

- ▶ t<sub>PLH</sub> Tempo de propagação de L para H na saída, desde a variação da entrada.

Prof. Nuno Roma

Sistemas Digitais 2015/16

## Tempos de Propagação

■ Exemplo (para TTL LS):

▶ Valores Típicos: 8 a 10 ns

▶ Valores Máximos: 15 a 20 ns

■ ATENÇÃO: Em geral, os tempos de propagação aumentam com o número de entradas ligadas à saída da porta lógica (fan-out).

Na determinação do atraso máximo na propagação de um sinal através de um circuito combinatório consideram-se, sempre, os valores máximos.

Prof. Nuno Roma

Sistemas Digitais 2015/16

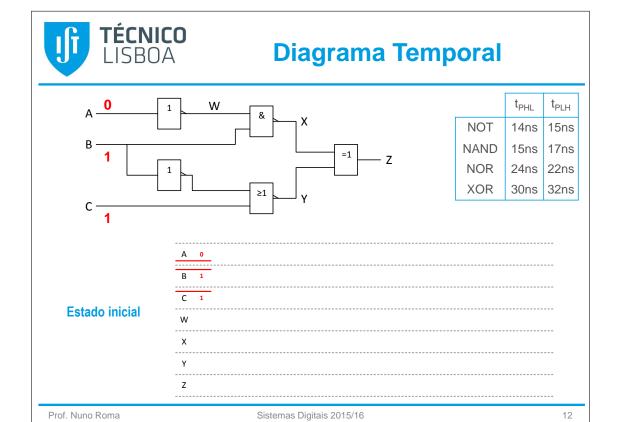

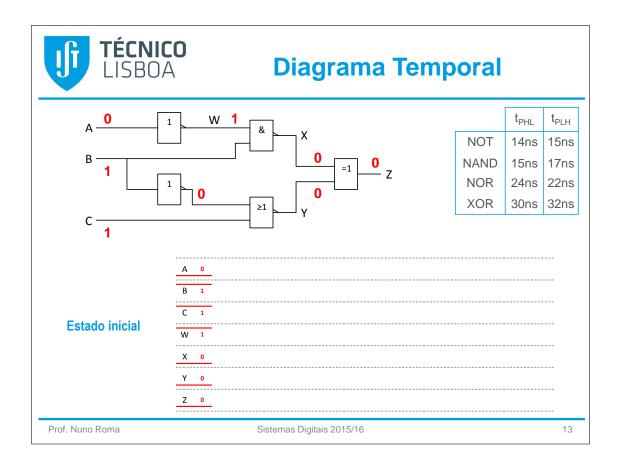

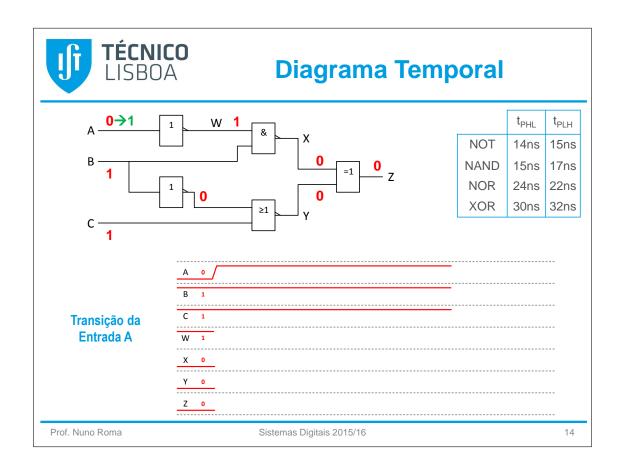

|      | t <sub>PHL</sub> | t <sub>PLH</sub> |

|------|------------------|------------------|

| NOT  | 14ns             | 15ns             |

| NAND | 15ns             | 17ns             |

| NOR  | 24ns             | 22ns             |

| XOR  | 30ns             | 32ns             |

O atraso máximo de um dado circuito é calculado como:

$$t_p = \max\{ t_{pLH} ; t_{pHL} \}$$

em que:

$\mathbf{t_{pLH}}\,$  - máximo tempo de propagação de uma qualquer entrada para a saída que leva a saída a transitar de Low para High

t<sub>pHL</sub> - máximo tempo de propagação de uma qualquer entrada para a saída que leva a saída a transitar de High para Low

|      | t <sub>PHL</sub> | t <sub>PLH</sub> |

|------|------------------|------------------|

| NOT  | 14ns             | 15ns             |

| NAND | 15ns             | 17ns             |

| NOR  | 24ns             | 22ns             |

| XOR  | 30ns             | 32ns             |

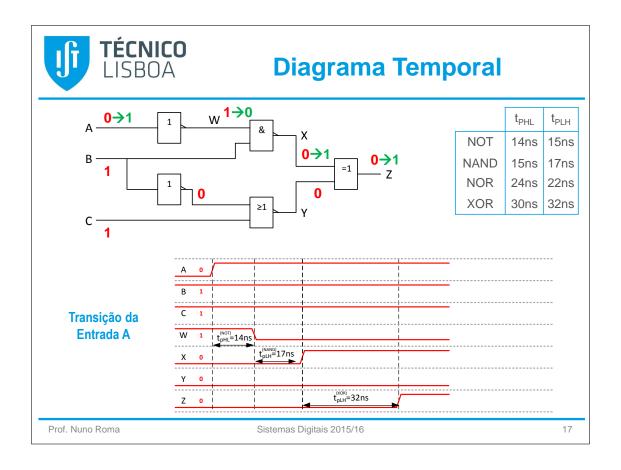

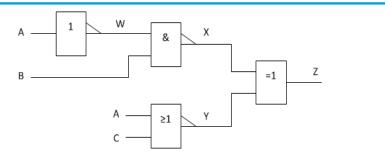

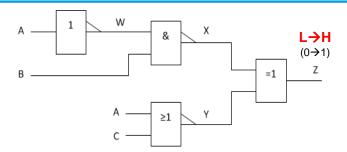

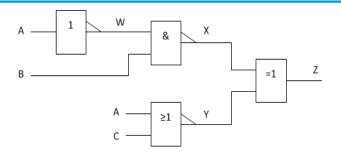

- O cálculo do tempo de propagação t<sub>pLH</sub> é calculado verificando todos os casos possíveis... E depois escolhendo o pior:

- 1. X=0

- ,  $Y=0 \rightarrow 1$

- 2.  $X=0 \rightarrow 1$

- . Y=0

- 3. X=1

- , Y=1  $\rightarrow$  0

- 4.  $X=1 \to 0$  , Y=1

Prof. Nuno Roma

Sistemas Digitais 2015/16

21

### Cálculo do Atraso Máximo

|      | t <sub>PHL</sub> | t <sub>PLH</sub> |

|------|------------------|------------------|

| NOT  | 14ns             | 15ns             |

| NAND | 15ns             | 17ns             |

| NOR  | 24ns             | 22ns             |

| XOR  | 30ns             | 32ns             |

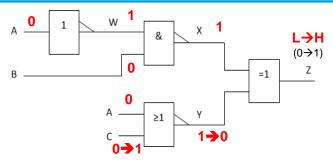

- O cálculo do tempo de propagação t<sub>pLH</sub> é calculado verificando todos os casos possíveis... E depois escolhendo o pior:

- X=0

3. X=1

$, Y=0 \rightarrow 1$

,  $Y=1 \rightarrow 0$

- 2.  $X=0 \rightarrow 1$

- , Y=1 4.  $X=1 \to 0$

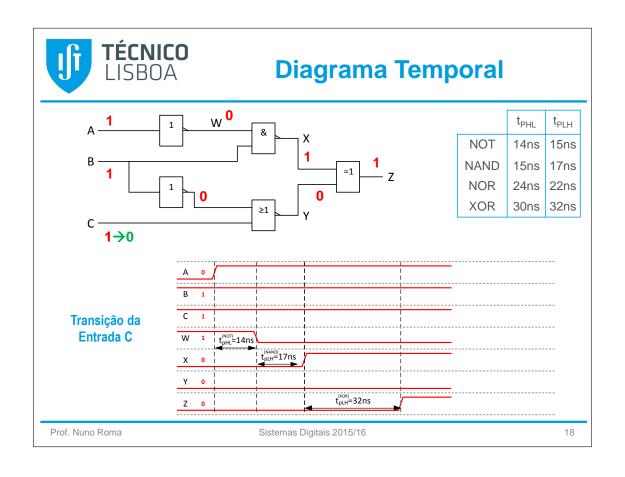

- $X=0 \rightarrow B=1, W=1, A=0$

- Logo C transita  $1 \rightarrow 0$

$t_{pLH} = t_{pLH}(NOR) + t_{pLH}(XOR) = 54ns$

Prof. Nuno Roma

Sistemas Digitais 2015/16

|      | t <sub>PHL</sub> | t <sub>PLH</sub> |

|------|------------------|------------------|

| NOT  | 14ns             | 15ns             |

| NAND | 15ns             | 17ns             |

| NOR  | 24ns             | 22ns             |

| XOR  | 30ns             | 32ns             |

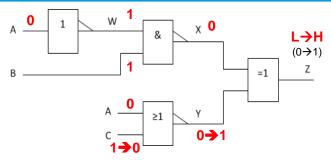

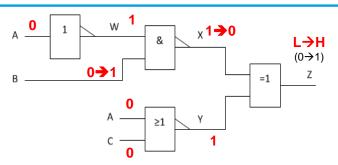

O cálculo do tempo de propagação t<sub>pLH</sub> é calculado verificando todos os casos possíveis... E depois escolhendo o <u>pior</u>:

, Y=1

O pior caso corresponde à transição vir da porta NOT:

A transita  $0 \rightarrow 1$

$t_{pLH} = t_{pHL}(NOT) + t_{pLH}(NAND) + t_{pLH}(XOR)$ = 14+17+32=63ns

4.  $X=1 \to 0$

Prof. Nuno Roma

Sistemas Digitais 2015/16

23

## Cálculo do Atraso Máximo

|      | t <sub>PHL</sub> | t <sub>PLH</sub> |

|------|------------------|------------------|

| NOT  | 14ns             | 15ns             |

| NAND | 15ns             | 17ns             |

| NOR  | 24ns             | 22ns             |

| XOR  | 30ns             | 32ns             |

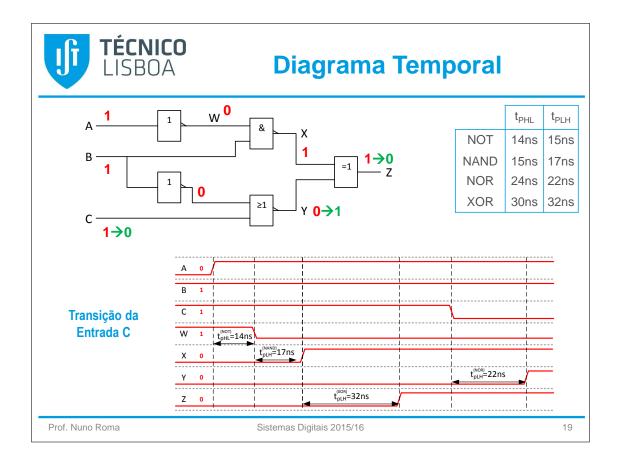

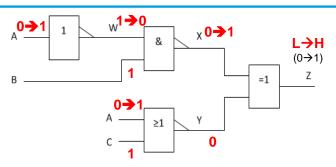

O cálculo do tempo de propagação t<sub>pLH</sub> é calculado verificando todos os casos possíveis... E depois escolhendo o <u>pior</u>:

,

$$Y=0 \rightarrow 1$$

2.

$$X=0 \rightarrow 1$$

,  $Y=$

$$, Y = 0$$

3.

$$X=1$$

,  $Y=1 \to 0$

4.

$$X=1 \to 0$$

,  $Y=1$

$$t_{pLH} = t_{pHL}(NOR) + t_{pLH}(XOR) =$$

= 24+32=56ns

Prof. Nuno Roma

Sistemas Digitais 2015/16

|      | $t_{PHL}$ | t <sub>PLH</sub> |

|------|-----------|------------------|

| NOT  | 14ns      | 15ns             |

| NAND | 15ns      | 17ns             |

| NOR  | 24ns      | 22ns             |

| XOR  | 30ns      | 32ns             |

- O cálculo do tempo de propagação t<sub>pLH</sub> é calculado verificando todos os casos possíveis... E depois escolhendo o pior:

- X=0

- ,  $Y=0 \rightarrow 1$

- 2.  $X=0 \rightarrow 1$

- . Y=0

- $, Y=1 \rightarrow 0$

- $t_{pLH} = t_{pHL}(NAND) + t_{pLH}(XOR) =$ = 15+32=47ns

Prof. Nuno Roma

Sistemas Digitais 2015/16

25

## Cálculo do Atraso Máximo

|      | t <sub>PHL</sub> | t <sub>PLH</sub> |

|------|------------------|------------------|

| NOT  | 14ns             | 15ns             |

| NAND | 15ns             | 17ns             |

| NOR  | 24ns             | 22ns             |

| XOR  | 30ns             | 32ns             |

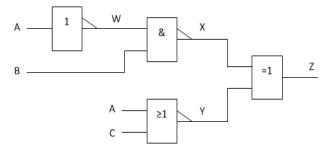

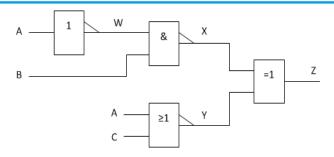

- O cálculo do tempo de propagação t<sub>pLH</sub> é calculado verificando todos os casos possíveis... E depois escolhendo o pior:

- 1. X=0

- ,  $Y=0 \rightarrow 1$

- $\rightarrow$   $t_{pLH} = 54$ ns

- 2.  $X=0 \to 1$

- , Y=0

- $\rightarrow$   $t_{pLH} = 63$ ns

- 3. X=1 ,  $Y=1 \rightarrow 0$

- $t_{pLH} = 56$ ns

- 4.  $X=1 \rightarrow 0$  , Y=1

- $\rightarrow$   $t_{pLH} = 47 ns$

Tempo de propagação

$t_{pLH} = 63 \text{ ns}$

Prof. Nuno Roma

Sistemas Digitais 2015/16

|      | t <sub>PHL</sub> | t <sub>PLH</sub> |

|------|------------------|------------------|

| NOT  | 14ns             | 15ns             |

| NAND | 15ns             | 17ns             |

| NOR  | 24ns             | 22ns             |

| XOR  | 30ns             | 32ns             |

- O cálculo do tempo de propagação t<sub>pLH</sub> é calculado verificando todos os casos possíveis... E depois escolhendo o <u>pior</u>:

- 1. X=0

- ,  $Y=0 \rightarrow 1$

- 2.  $X=0 \rightarrow 1$

- , Y=0

- 3. X=1

- , Y=1  $\rightarrow$  0

- 4.  $X=1 \to 0$

- , Y=1

- Ver todos os casos possíveis...

- verificar qual é o pior!!!

Prof. Nuno Roma

Sistemas Digitais 2015/16

27

### Cálculo do Atraso Máximo

|      | t <sub>PHL</sub> | t <sub>PLH</sub> |

|------|------------------|------------------|

| NOT  | 14ns             | 15ns             |

| NAND | 15ns             | 17ns             |

| NOR  | 24ns             | 22ns             |

| XOR  | 30ns             | 32ns             |

O atraso máximo de um dado circuito é calculado como:

$$t_p = max\{t_{pLH}; t_{pHL}\}$$

em que:

$\mathbf{t_{pLH}}\,$  - máximo tempo de propagação de uma qualquer entrada para a saída que leva a saída a transitar de Low para High

t<sub>pHL</sub> - máximo tempo de propagação de uma qualquer entrada para a saída que leva a saída a transitar de High para Low

Prof. Nuno Roma

Sistemas Digitais 2015/16

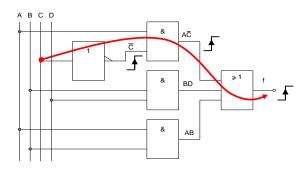

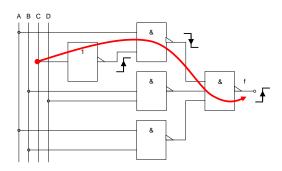

## Cálculo do Caminho com Atraso de Propagação Máximo

#### **Exemplo:**

O caminho de atraso máximo é activado quando C comuta e A=1, B.D=0 e A.B=0.

$$\begin{split} t_{PLHtotal} &= t_{PLHnot} + t_{PLHand} + t_{PLHor} \\ &\quad \text{ou} \\ t_{PHLtotal} &= t_{PHLnot} + t_{PHLand} + t_{PHLor} \end{split}$$

Prof. Nuno Roma Sistemas Digitais 2015/16

## Cálculo do Caminho com Atraso de Propagação Máximo

#### Exemplo (cont.):

29

| ABCD |    |       |

|------|----|-------|

|      |    | J     |

|      | Ē. | \$1 f |

|     | t <sub>PHL</sub> | t <sub>PLH</sub> |

|-----|------------------|------------------|

| NOT | 14ns             | 15ns             |

| AND | 17ns             | 20ns             |

| OR  | 24ns             | 22ns             |

$$t_{P \text{ max}} = \max (14ns + 17ns + 24ns; 15ns + 20ns + 22ns)$$

=  $\max (55ns; 57ns) = 57ns$

Prof. Nuno Roma Sistemas Digitais 2015/16 30

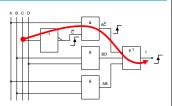

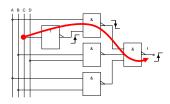

# Cálculo do Caminho com Atraso de Propagação Máximo (com NANDs)

#### **Exemplo:**

O caminho de atraso máximo é activado quando C comuta e A=1, B.D=1 e A.B=1.

$$\begin{split} t_{PLHtotal} &= t_{PLHnot} + t_{PHLnand1} + t_{PLHnand2} \\ & \text{ou} \\ t_{PHLtotal} &= t_{PHLnot} + t_{PLHnand1} + t_{PHLnand2} \end{split}$$

Prof. Nuno Roma

Sistemas Digitais 2015/16

31

# Cálculo do Caminho com Atraso de Propagação Máximo (com NANDs)

#### Exemplo (cont.)

|      | t <sub>PHL</sub> | t <sub>PLH</sub> |

|------|------------------|------------------|

| NOT  | 14ns             | 15ns             |

| NAND | 17ns             | 16ns             |

$$t_{P \text{ max}} = \max (14ns + 16ns + 17ns; 15ns + 17ns + 16ns)$$

=  $\max (47ns; 48ns) = 48ns$

Prof. Nuno Roma

Sistemas Digitais 2015/16

## **DISPOSITIVOS LÓGICOS ESPECIAIS**

Prof. Nuno Roma

Sistemas Digitais 2015/16

33

## **Dispositivos Especiais**

- Para além das portas básicas, existem outros dispositivos lógicos que são importantes para garantir certo tipo de funcionalidades:

- ▶ Buffers de três estados (tri-state)

- ▶ Portas de passagem (*transmission gates*)

Prof. Nuno Roma

Sistemas Digitais 2015/16

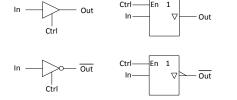

#### **Buffers de Três Estados**

#### ■ Buffer de três estados (tri-state):

- Dispositivo que, para além de uma entrada e uma saída de dados, dispõe ainda de uma entrada de controlo que define o comportamento da saída:

- Controlo = H → o valor da saída é igual ao valor que se apresenta na entrada de dados;

- Controlo = L → o porto de saída fica em alta impedância, i.e., a saída fica desligada electricamente.

| Ctrl | In | Out       | Out       |

|------|----|-----------|-----------|

| L    | Χ  | Desligada | Desligada |

| Н    | L  | L         | Н         |

| Н    | Н  | Н         | L         |

|      |    |           |           |

Prof. Nuno Roma Sistemas Digitais 2015/16 35

#### **Buffers de Três Estados**

#### ■ Exemplos de aplicação:

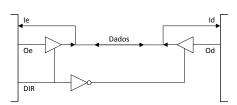

► Linha Bidireccional:

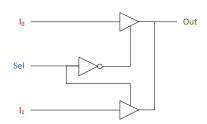

▶ Selecção de Sinais:

Prof. Nuno Roma Sistemas Digitais 2015/16 3

## Portas de Passagem

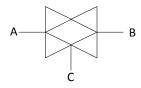

#### ■ Portas de Passagem (*transmission-gates*):

▶ Permite, quando activada, a passagem de sinais em <u>ambos os</u> <u>sentidos</u> e em <u>toda a gama de tensão</u>, i.e., permite a passagem de sinais dentro ou fora dos níveis digitais da família lógica considerada (ex: CMOS, TTL, etc.) :

Prof. Nuno Roma

Sistemas Digitais 2015/16

37

## Próxima Aula

## Próxima Aula

#### Tema da Próxima Aula:

- ► Circuitos combinatórios típicos:

- Descodificadores

- Codificadores

- Multiplexeres

- Demultiplexeres

Prof. Nuno Roma

Sistemas Digitais 2015/16

39

## Agradecimentos

Algumas páginas desta apresentação resultam da compilação de várias contribuições produzidas por:

- Guilherme Arroz

- Horácio Neto

- Nuno Horta

- Pedro Tomás

Prof. Nuno Roma

Sistemas Digitais 2015/16