# SISTEMAS DIGITAIS (SD)

#### **MEEC**

### Acetatos das Aulas Teóricas

Versão 4.0 - Português

#### Aula Nº 19:

Título: Síntese de Circuitos Sequenciais: Minimização do Número de Estados

Sumário: Especificação e projecto de circuitos sequenciais síncronos: Minimização do

número de estados; Exemplo (Mealy).

2015/2016

Nuno.Roma@tecnico.ulisboa.pt

# Sistemas Digitais (SD)

### Síntese de Circuitos Sequenciais: Minimização do Número de Estados

## **Aula Anterior**

#### Na aula anterior:

- ▶ Definição de circuito sequencial síncrono

- ► Máquinas de Mealy e de Moore

- ► Especificação de circuitos sequenciais síncronos:

- Diagrama de estados

- ▶ Projecto de circuitos sequenciais síncronos:

- Codificação dos estados

- Tabela de transição de estados

- Determinação das funções lógicas de saída e estado seguinte

## **Planeamento**

| SEMANA          | TEÓRICA 1                                                                          | TEÓRICA 2                                                          | PROBLEMAS/LABORATÓRIO |  |

|-----------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------|--|

| 14/Set a 19/Set | Introdução                                                                         | Sistemas de Numeração e Códigos                                    |                       |  |

| 21/Set a 26/Set | Álgebra de Boole                                                                   | Elementos de Tecnologia                                            | P0                    |  |

| 28/Set a 3/Out  | Funções Lógicas                                                                    | Minimização de Funções Booleanas (I)                               | LO                    |  |

| 5/Out a 10/Out  | Minimização de Funções Booleanas (II)                                              | Def. Circuito Combinatório; Análise Temporal                       | P1                    |  |

| 12/Out a 17/Out | Circuitos Combinatórios (I) – Codif., MUXs, etc.                                   | Circuitos Combinatórios (II) - Som., Comp., etc.                   | L1                    |  |

| 19/Out a 24/Out | Circuitos Combinatórios (III) - ALUs                                               | Linguagens de Descrição e Simulação de<br>Circuitos Digitais       | P2                    |  |

| 26/Out a 31/Out | Circuitos Sequenciais: Latches                                                     | Circuitos Sequenciais: Flip-Flops                                  | L2                    |  |

| 2/Nov a 7/Nov   | Caracterização Temporal                                                            | Registos                                                           | P3                    |  |

| 9/Nov a 14/Nov  | Revisões Teste 1                                                                   | Contadores                                                         | L3                    |  |

| 16/Nov a 21/Nov | Síntese de Circuitos Sequenciais: Definições                                       | Síntese de Circuitos Sequenciais: Minimização do número de estados | P4                    |  |

| 23/Nov a 28/Nov | Síntese de Circuitos Sequenciais: Síntese com Contadores                           | Memórias                                                           | L4                    |  |

| 30/Nov a 5/Dez  | Máq. Estado Microprogramadas: Circuito de<br>Dados e Circuito de Controlo          | Máq. Estado Microprogramadas:<br>Endereçamento Explícito/Implícito | P5                    |  |

| 7/Dez a 12/Dez  | Circuitos de Controlo, Transferência e<br>Processamento de Dados de um Processador | Lógica Programável                                                 | L5                    |  |

| 14/Dez a 18/Dez | P6                                                                                 | P6                                                                 | L6                    |  |

Prof. Nuno Roma

Sistemas Digitais 2015/16

3

## Sumário

## ■ Tema da aula de hoje:

- ▶ Especificação e projecto de circuitos sequenciais síncronos:

- Minimização do número de estados

- ► Exemplo (Mealy)

## Bibliografia:

- M. Mano, C. Kime: Secções 5.4 a 5.7

- G. Arroz, J. Monteiro, A. Oliveira: Secção 7.1 a 7.4

### Revisão: circuito combinatório vs circuito sequencial

#### ▶ Circuito Combinatório

• O valor da saída depende apenas do valor nas entradas nesse instante

#### ► Circuito Sequencial

- O valor da saída depende do valor actual nas entradas, bem como da história anterior dos estados do circuito

- o Como? → através de elementos de memória (ex: latches e flip-flops)

- Podem ser divididos em:

- o Síncronos: o sinal de relógio sincroniza toda a actividade do circuito

- Assíncronos: não usam sinal de relógio as transições de estado ocorrem sempre que há uma alteração nas entradas do circuito

Prof. Nuno Roma

Sistemas Digitais 2015/16

5

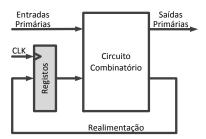

## Síntese de Circuitos Síncronos

■ Revisão: Circuito Sequencial Síncrono

#### ▶ Duas componentes:

- Bloco de lógica puramente combinatória

- Implementa as funções necessárias para que o circuito tenha a transição entre estados pretendida

- Elementos de memória, controlados por um sinal de relógio

- o Mantém o estado do circuito ao longo do tempo

Prof. Nuno Roma Sistemas Digitais 2015/16

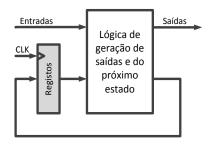

### Revisão: Máquinas de Moore vs. Máquinas de Mealy

- ▶ As máquinas de estado síncronas podem ser dividias em:

- **Máquinas de Moore**: a saída depende *apenas* das variáveis de <u>estado</u> actuais;

- Máquinas de Mealy: a saída é função das variáveis de <u>estado</u> actuais e do valor das <u>entradas</u> presentes no circuito

Prof. Nuno Roma

Sistemas Digitais 2015/16

7

## Síntese de Circuitos Síncronos

### Projecto de Circuitos Sequenciais Síncronos

- **▶** Procedimento:

- Especificação formal:

- Diagrama de estados

- o Fluxograma

- Simplificação da especificação

- Projecto:

- 1. Codificação dos estados

- 2. Tabelas de transição de estados

- 3. Determinação das funções lógicas de saída e estado seguinte

Prof. Nuno Roma

Sistemas Digitais 2015/16

### Projecto de Circuitos Sequenciais Síncronos

#### ▶ Procedimento:

- Especificação formal:

- Diagrama de estados

- Fluxograma

#### Simplificação da especificação

- Projecto:

- 1. Codificação dos estados

- 2. Tabelas de transição de estados

- 3. Determinação das funções lógicas de saída e estado seguinte

Prof. Nuno Roma

Sistemas Digitais 2015/16

9

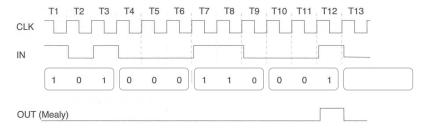

## Simplificação da Especificação

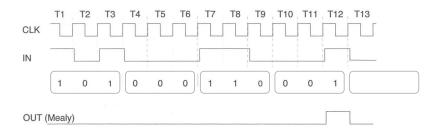

### ■ Exemplo – Detector de Paridade

- ▶ Pretende-se enviar dados por uma linha, em grupos de 3 bits. A linha está sujeita a ruído, pelo que se implementou um protocolo de detecção de erros que garante que cada grupo de 3 bits tem um número par de bits a 1.

- O circuito sequencial pretendido deverá assinalar na sua saída sempre que ocorrer um erro de transmissão, identificado por um número ímpar de bits num grupo de 3 bits

Prof. Nuno Roma

Sistemas Digitais 2015/16

### ■ Exemplo – Detector de Paridade

#### ▶ Problema:

- Como construir o diagrama de estados?

- A solução é única?

- É possível optimizar o número de estados?

Prof. Nuno Roma

Sistemas Digitais 2015/16

11

## Simplificação da Especificação

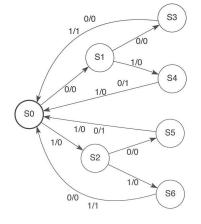

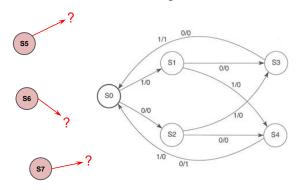

### Construção do Diagrama de Estados

- O diagrama de estados pode ser construído directamente a partir da definição do problema:

- Enumerar todas as possíveis combinações de estados que podem ocorrer a partir do estado de Reset (S0), e gerar o valor 1 na saída quando o número de 1's for ímpar, retornando ao estado S0 para processar a próxima sequência de 3 bits.

Prof. Nuno Roma

Sistemas Digitais 2015/16

### Construção do Diagrama de Estados

- ▶ Este diagrama de estados pode ser simplificado?

- ▶ Existem *estados equivalentes* que podem ser fundidos?

#### Definição:

Dois estados dizem-se <u>estados equivalentes</u> se, e só se, para cada combinação possível nas entradas, eles geram a mesma saída e transitam para o mesmo estado ou para estados que também sejam equivalentes.

Prof. Nuno Roma

Sistemas Digitais 2015/16

13

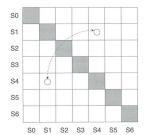

## Simplificação da Especificação

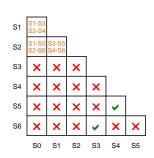

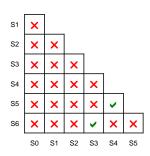

## ■ Tabela de Implicações

- ▶ Uma linha e uma coluna por estado;

- ▶ Indica quais os pares de estados que são equivalentes;

- Uma vez que esta matriz é simétrica, apenas se considera a componente inferior à diagonal principal:

- Exemplo: S1  $\leftrightarrow$  S4  $\Leftrightarrow$  S4  $\leftrightarrow$  S1

Prof. Nuno Roma

Sistemas Digitais 2015/16

### Tabela de Implicações

▶ 1º Passo: identificar os pares de estados que não podem ser equivalentes, porque geram saídas diferentes para a mesma entrada.

#### Exemplos:

- Os estados S0 e S6 são necessariamente não equivalentes, porque geram saídas diferentes para a entrada 1

- O estado S0, cuja saída é sempre 0, não pode ser equivalente ao estado S3, pois este gera 1 na sua saída quando a entrada é 1; Idem para os estados S4, S5 ou S6.

Prof. Nuno Roma

Sistemas Digitais 2015/16

## Simplificação da Especificação

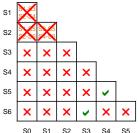

## Tabela de Implicações

▶ 2º Passo: identificar os pares de estados que são equivalentes, pois não só geram as mesmas saídas, como transitam para os mesmos estados (ou equivalentes).

#### Exemplos:

• Os estados S4 e S5 são equivalentes, porque têm as mesmas saídas, para ambos os valores de entrada, e transitam para o estado S0, para ambos os valores de entrada; Idem para os estados S3 e S6.

### ■ Tabela de Implicações

▶ 3º Passo: identificar os pares de estados que poderão ser equivalentes caso outros pares também o sejam.

#### Exemplos:

Os estados S1 e S2 apenas poderão ser equivalentes se os estados S3 e S5 forem equivalentes e se os estados S4 e S6 forem equivalentes

a entrada correspondente ao par (S1,S2) deve ser preenchida com os pares (S3,S5) e (S4,S6)

Prof. Nuno Roma

Sistemas Digitais 2015/16

17

## Simplificação da Especificação

### ■ Tabela de Implicações

▶ 4º Passo: eliminar, através de passagens sucessivas da tabela, os elementos que não podem ser equivalentes, dado que a sua equivalência depende da equivalência de outros estados que a tabela indica como não sendo equivalentes.

#### Exemplos:

- O par (S0,S1) não pode ser equivalente, porque depende do par (S1,S3) que a tabela mostra como sendo não equivalente

- O par (S0,S2) não pode ser equivalente, porque depende do par (S1,S5) que a tabela mostra como sendo não equivalente

- O par (S1,S2) não pode ser equivalente, porque depende do par (S3,S5) que a tabela mostra como sendo não equivalente

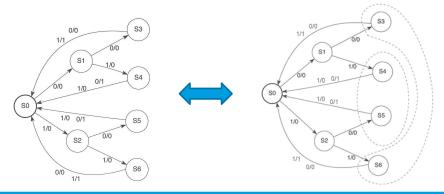

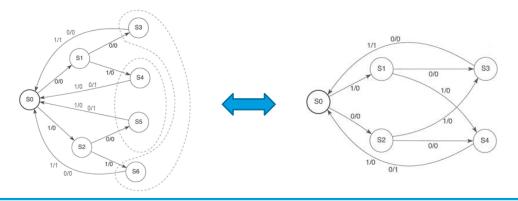

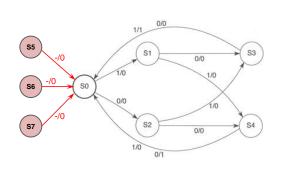

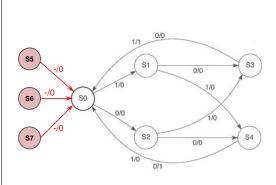

### Simplificação do Diagrama de Estados

- ▶ De acordo com o processo de simplificação realizado, conclui-se que:

- O estado S3 é equivalente ao estado S6

- O estado S4 é equivalente ao estado S5

Prof. Nuno Roma

Sistemas Digitais 2015/16

19

## Simplificação da Especificação

## Simplificação do Diagrama de Estados

- ▶ De acordo com o processo de simplificação realizado, conclui-se que:

- O estado S3 é equivalente ao estado S6

- O estado S4 é equivalente ao estado S5

Prof. Nuno Roma

Sistemas Digitais 2015/16

### Simplificação do Diagrama de Estados

- ▶ De acordo com o processo de simplificação realizado, conclui-se que:

- O estado S3 é equivalente ao estado S6

- O estado S4 é equivalente ao estado S5

Prof. Nuno Roma Sistemas Digitais 2015/16 21

## Síntese de Circuitos Síncronos

### Projecto de Circuitos Sequenciais Síncronos

#### **▶** Procedimento:

- Especificação formal:

- Diagrama de estados

- o Fluxograma

- Simplificação da especificação

- Projecto:

- 1. Codificação dos estados

- 2. Tabelas de transição de estados

- 3. Determinação das funções lógicas de saída e estado seguinte

Prof. Nuno Roma

Sistemas Digitais 2015/16

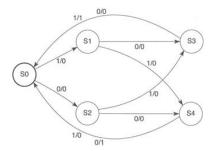

### Codificação dos Estados

▶ Considerando a existência de 5 estados  $(S_0, S_1, S_2, S_3, S_4)$ , a codificação usando código binário natural irá usar k flip-flops, em que  $k = \lceil \log_2(5) \rceil = \lceil 2.321 \rceil = 3$

| E-t-d-                           | Codificação |       |       |  |  |

|----------------------------------|-------------|-------|-------|--|--|

| Estado                           | $Q_2$       | $Q_1$ | $Q_0$ |  |  |

| $S_0$                            | 0           | 0     | 0     |  |  |

| S <sub>1</sub>                   | 0           | 0     | 1     |  |  |

| $S_2$                            | 0           | 1     | 0     |  |  |

| S <sub>2</sub><br>S <sub>3</sub> | 0           | 1     | 1     |  |  |

| S <sub>4</sub>                   | 1           | 0     | 0     |  |  |

Prof. Nuno Roma Sistemas Digitais 2015/16 23

## Síntese de Circuitos Síncronos

## ■ Tabela de Transição de Estados

| Entradas | da Tabela          | Saídas da Tabela   |       |  |

|----------|--------------------|--------------------|-------|--|

| Entrada  | Estado<br>Presente | Estado<br>Seguinte | Saída |  |

| 0        | S <sub>0</sub>     | $S_2$              | 0     |  |

| 1        | S <sub>0</sub>     | S <sub>1</sub>     | 0     |  |

| 0        | S <sub>1</sub>     | $S_3$              | 0     |  |

| 1        | S <sub>1</sub>     | $S_4$              | 0     |  |

| 0        | $S_2$              | $S_4$              | 0     |  |

| 1        | $S_2$              | $S_3$              | 0     |  |

| 0        | $S_3$              | $S_0$              | 0     |  |

| 1        | $S_3$              | S <sub>0</sub>     | 1     |  |

| 0        | S <sub>4</sub>     | S <sub>0</sub>     | 1     |  |

| 1        | S <sub>4</sub>     | S <sub>0</sub>     | 0     |  |

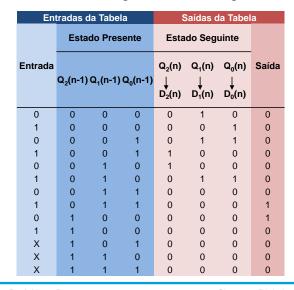

- ▶ O que acontece se a máquina transitar para um estado inválido  $(S_5,S_6,S_7)? \rightarrow Lock-out!!!$

- ► **Solução**: obrigar a máquina a transitar para um estado válido (ex: S₀)

Prof. Nuno Roma Sistemas Digitais 2015/16 24

## ■ Tabela de Transição de Estados

|   | Entradas da Tabela |                                  | Saldas da Tabela                                                                          |       |  |

|---|--------------------|----------------------------------|-------------------------------------------------------------------------------------------|-------|--|

|   | Entrada            | Estado<br>Presente               | Estado<br>Seguinte                                                                        | Saída |  |

|   | 0                  | S <sub>0</sub>                   | $S_2$                                                                                     | 0     |  |

|   | 1                  | S <sub>0</sub><br>S <sub>1</sub> | S <sub>1</sub>                                                                            | 0     |  |

|   | 0                  |                                  | S <sub>1</sub><br>S <sub>3</sub><br>S <sub>4</sub>                                        | 0     |  |

|   | 1                  | S <sub>1</sub>                   | $S_4$                                                                                     | 0     |  |

|   | 0                  | S <sub>2</sub><br>S <sub>2</sub> | $S_4$                                                                                     | 0     |  |

|   | 1                  | $S_2$                            | $S_3$                                                                                     | 0     |  |

|   | 0                  | S <sub>3</sub><br>S <sub>3</sub> | S <sub>4</sub> S <sub>3</sub> S <sub>0</sub> S <sub>0</sub> S <sub>0</sub> S <sub>0</sub> | 0     |  |

|   | 1                  | $S_3$                            | $S_0$                                                                                     | 1     |  |

|   | 0                  | $S_4$                            | $S_0$                                                                                     | 1     |  |

|   | 1                  | $S_4$                            | $S_0$                                                                                     | 0     |  |

|   | X                  | S <sub>5</sub>                   | $S_0$                                                                                     | 0     |  |

|   | Х                  | S <sub>6</sub><br>S <sub>7</sub> | S <sub>0</sub><br>S <sub>0</sub><br>S <sub>0</sub>                                        | 0     |  |

| , | Х                  | S <sub>7</sub>                   | $S_0$                                                                                     | 0     |  |

|   |                    |                                  |                                                                                           |       |  |

25

Preenchimento com os estados adicionais, para evitar situações de Lock-out

Prof. Nuno Roma Sistemas Digitais 2015/16

## Síntese de Circuitos Síncronos

## ■ Tabela de Transição de Estados

| Entradas da Tabela |                      |                      | Saídas da Tabela     |                    |                    |                    |       |  |

|--------------------|----------------------|----------------------|----------------------|--------------------|--------------------|--------------------|-------|--|

| Entrada            | Estado Presente      |                      | Estado Seguinte      |                    |                    | O-fal-             |       |  |

|                    | Q <sub>2</sub> (n-1) | Q <sub>1</sub> (n-1) | Q <sub>0</sub> (n-1) | Q <sub>2</sub> (n) | Q <sub>1</sub> (n) | Q <sub>0</sub> (n) | Saída |  |

| 0                  | 0                    | 0                    | 0                    | 0                  | 1                  | 0                  | 0     |  |

| 1                  | 0                    | 0                    | 0                    | 0                  | 0                  | 1                  | 0     |  |

| 0                  | 0                    | 0                    | 1                    | 0                  | 1                  | 1                  | 0     |  |

| 1                  | 0                    | 0                    | 1                    | 1                  | 0                  | 0                  | 0     |  |

| 0                  | 0                    | 1                    | 0                    | 1                  | 0                  | 0                  | 0     |  |

| 1                  | 0                    | 1                    | 0                    | 0                  | 1                  | 1                  | 0     |  |

| 0                  | 0                    | 1                    | 1                    | 0                  | 0                  | 0                  | 0     |  |

| 1                  | 0                    | 1                    | 1                    | 0                  | 0                  | 0                  | 1     |  |

| 0                  | 1                    | 0                    | 0                    | 0                  | 0                  | 0                  | 1     |  |

| 1                  | 1                    | 0                    | 0                    | 0                  | 0                  | 0                  | 0     |  |

| X                  | 1                    | 0                    | 1                    | 0                  | 0                  | 0                  | 0     |  |

| X                  | 1                    | 1                    | 0                    | 0                  | 0                  | 0                  | 0     |  |

| X                  | 1                    | 1                    | 1                    | 0                  | 0                  | 0                  | 0     |  |

Prof. Nuno Roma Sistemas Digitais 2015/16

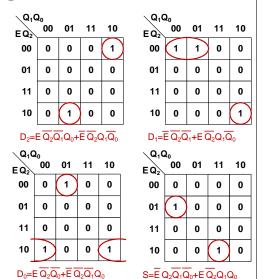

### Determinação das Funções Lógicas

Prof. Nuno Roma

Prof. Nuno Roma

Sistemas Digitais 2015/16

27

28

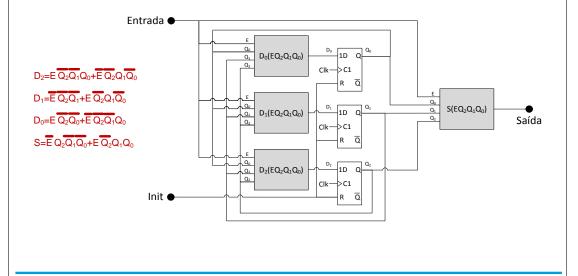

### Circuito Lógico

Sistemas Digitais 2015/16

## Próxima Aula

#### ■ Tema da Próxima Aula:

- ► Exemplo (Moore)

- ▶ Projecto de circuitos sequenciais baseados em contadores

Prof. Nuno Roma

Sistemas Digitais 2015/16

29

## Agradecimentos

Algumas páginas desta apresentação resultam da compilação de várias contribuições produzidas por:

- Guilherme Arroz

- Horácio Neto

- Nuno Horta

- Pedro Tomás

Prof. Nuno Roma

Sistemas Digitais 2015/16