# SISTEMAS DIGITAIS (SD)

#### **MEEC**

### Acetatos das Aulas Teóricas

Versão 4.0 - Português

#### Aula Nº 25:

Título: Lógica Programável

Sumário: Lógica programável (ROM, PLA, PAL e FPGA); Linguagens de descrição de

hardware (VHDL).

2015/2016

Nuno.Roma@tecnico.ulisboa.pt

# Sistemas Digitais (SD)

### Lógica Programável

### **Aula Anterior**

#### Na aula anterior:

- ▶ Circuitos de controlo, transferência e processamento de dados

- ▶ Exemplo de uma arquitectura simples de um processador

### **Planeamento**

| SEMANA          | TEÓRICA 1                                                                          | TEÓRICA 2                                                          | PROBLEMAS/LABORATÓRIO |

|-----------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------|

| 14/Set a 19/Set | Introdução                                                                         | Sistemas de Numeração e Códigos                                    |                       |

| 21/Set a 26/Set | Álgebra de Boole                                                                   | Elementos de Tecnologia                                            | P0                    |

| 28/Set a 3/Out  | Funções Lógicas                                                                    | Minimização de Funções Booleanas (I)                               | LO                    |

| 5/Out a 10/Out  | Minimização de Funções Booleanas (II)                                              | Def. Circuito Combinatório; Análise Temporal                       | P1                    |

| 12/Out a 17/Out | Circuitos Combinatórios (I) – Codif., MUXs, etc.                                   | Circuitos Combinatórios (II) - Som., Comp., etc.                   | L1                    |

| 19/Out a 24/Out | Circuitos Combinatórios (III) - ALUs                                               | Linguagens de Descrição e Simulação de<br>Circuitos Digitais       | P2                    |

| 26/Out a 31/Out | Circuitos Sequenciais: Latches                                                     | Circuitos Sequenciais: Flip-Flops                                  | L2                    |

| 2/Nov a 7/Nov   | Caracterização Temporal                                                            | Registos                                                           | P3                    |

| 9/Nov a 14/Nov  | Revisões Teste 1                                                                   | Contadores                                                         | L3                    |

| 16/Nov a 21/Nov | Síntese de Circuitos Sequenciais: Definições                                       | Síntese de Circuitos Sequenciais: Minimização do número de estados | P4                    |

| 23/Nov a 28/Nov | Síntese de Circuitos Sequenciais: Síntese com Contadores                           | Memórias                                                           | L4                    |

| 30/Nov a 5/Dez  | Máq. Estado Microprogramadas: Circuito de<br>Dados e Circuito de Controlo          | Máq. Estado Microprogramadas:<br>Endereçamento Explícito/Implícito | P5                    |

| 7/Dez a 12/Dez  | Circuitos de Controlo, Transferência e<br>Processamento de Dados de um Processador | Lógica Programável                                                 | L5                    |

| 14/Dez a 18/Dez | P6                                                                                 | P6                                                                 | L6                    |

Prof. Nuno Roma

Sistemas Digitais 2015/16

3

### **Sumário**

### ■ Tema da aula de hoje:

- ► Lógica programável:

- ROM

- PLA

- PAL

- FPGA

- ▶ Linguagens de descrição de hardware

- VHDL

### **□** Bibliografia:

G. Arroz, C. Sêrro, "Sistemas Digitais: Apontamentos das Aulas Teóricas", IST, 2005: Capítulo 18 (disponível no Fenix)

# **Programmable Logic Device**

### ■ PLD: Programmable Logic Device

- Vários dispositivos disponíveis com a possibilidade de programação da função lógica implementada:

- ROM: Read-Only Memory (ROM, PROM, EPROM, EEPROM, etc...)

- PLA: Programmable Logic Array

- PAL: Programmable Array Logic

- FPGA: Field Programmable Gate Array

- ► Função: implementação, num só circuito integrado, de circuitos com lógica combinatória (e/ou sequencial) de média complexidade, que de outra forma seriam implementados com vários circuitos integrados.

Prof. Nuno Roma

Sistemas Digitais 2015/16

5

# **Read Only Memory (ROM)**

### ROM: Read-Only Memory

- ▶ Diferentes famílias disponíveis:

- ROM mask programmable ROM

- PROM field Programmable ROM

- EPROM Erasable Programmable ROM

- EEPROM Electrically Erasable Programmable ROM

Prof. Nuno Roma Sistemas Digitais 2015/16

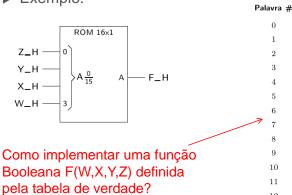

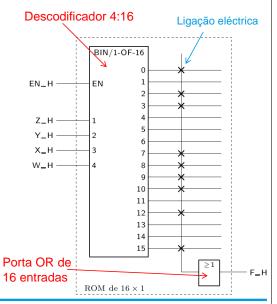

#### ■ ROM: Read-Only Memory

| '_H :<br>A3 | X_H<br>A2 | Y_H<br>A1 | Z_H<br>A0 | Dados |

|-------------|-----------|-----------|-----------|-------|

| L           | L         | L         | L         | Н     |

| L           | L         | L         | H         | L     |

| L           | L         | H         | L         | Н     |

| L           | L         | H         | H         | Н     |

| L           | Н         | L         | L         | L     |

| L           | Н         | L         | H         | L     |

| L           | H         | H         | L         | L     |

| L           | H         | Н         | H         | Н     |

| Н           | L         | L         | L         | Н     |

| H           | L         | L         | H         | Н     |

| H           | L         | H         | L         | Н     |

| H           | L         | Н         | H         | L     |

| H           | Н         | L         | L         | Н     |

| H           | Н         | L         | H         | L     |

| Н           | H         | H         | L         | L     |

| H           | H         | H         | H         | Н     |

|             |           |           |           |       |

Prof. Nuno Roma

Sistemas Digitais 2015/16

12

1415

# Read Only Memory (ROM)

### ■ ROM: Read-Only Memory

|           |           |            |            |                 | T     |

|-----------|-----------|------------|------------|-----------------|-------|

| Palavra # | W_H<br>A3 | X_H<br>A2  | Y_H<br>A1  | Z_H<br>A0       | Dados |

| 0         | L         | L          | L          | L               | Н     |

| 1         | L         | $_{\rm L}$ | L          | $_{\mathrm{H}}$ | L     |

| 2         | L         | L          | Н          | L               | Н     |

| 3         | L         | L          | Н          | H               | Н     |

| 4         | L         | Н          | L          | L               | L     |

| 5         | L         | Н          | L          | $_{\mathrm{H}}$ | L     |

| 6         | L         | H          | H          | L               | L     |

| 7         | L         | Н          | H          | H               | Н     |

| 8         | Н         | L          | L          | L               | Н     |

| 9         | Н         | L          | L          | H               | Н     |

| 10        | Н         | L          | Н          | L               | Н     |

| 11        | Н         | L          | Н          | H               | L     |

| 12        | Н         | H          | L          | L               | Н     |

| 13        | Н         | H          | $_{\rm L}$ | H               | L     |

| 14        | Н         | Н          | Н          | L               | L     |

| 15        | Н         | Н          | Н          | H               | Н     |

Prof. Nuno Roma

Sistemas Digitais 2015/16

# **Read Only Memory (ROM)**

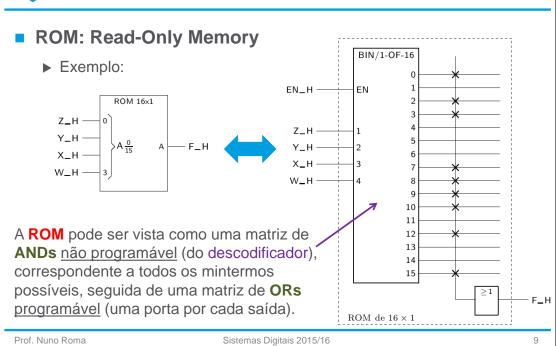

### ■ ROM: Read-Only Memory

- ▶ Ao contrário de outros dispositivos (ver a seguir), a ROM não impõe restrições no número de mintermos gerados (2<sup>n</sup>) e agrupados.

- ▶ Exemplo:

- uma ROM de 8k x 8 bits pode implementar, no máximo, 8 funções booleanas simples (uma por cada saída) de 13 variáveis Booleanas (porque 8k = 2<sup>13</sup>).

Prof. Nuno Roma

#### ROM: Read-Only Memory

- ▶ Exemplos de aplicação:

- Implementação de funções Booleanas combinatórias (genéricas);

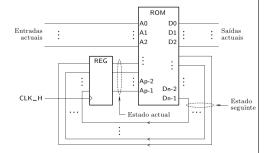

- Implementação de sistemas sequenciais micro-programados;

- Armazenamento, em memória não volátil, de programas executados por processadores;

- Exemplo: configuração do sistema de interface de entradas e saídas (BIOS) de um computador.

Prof. Nuno Roma

Sistemas Digitais 2015/16

11

# **Read Only Memory (ROM)**

### ■ ROM: Read-Only Memory

#### ▶ Vantagens:

- Facilidade e rapidez de definição do seu conteúdo a partir da tabela de verdade da função;

- Existe software para programação automática;

- Pouco dispendiosas.

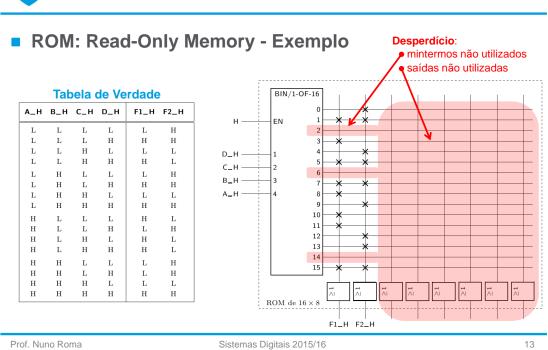

#### ▶ Desvantagens:

- Uma vez que gera todos os mintermos para o conjunto de variáveis de entrada, conduz a desperdício de recursos, caso esses mintermos não seja utilizados pela função;

- Quando o número de entradas é muito elevado, pode tornar-se impraticável a utilização de ROMs, devido à limitação do número de entradas:

- Mais <u>lenta</u> e consome mais <u>energia</u> do que circuitos dedicados.

Prof. Nuno Roma Sistemas Digitais 2015/16 12

# **Programmable Logic Array (PLA)**

### ■ PLA: Programmable Logic Array

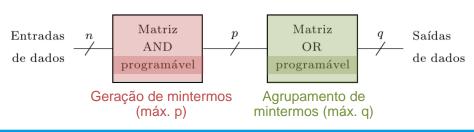

- ▶ Para ultrapassar os inconvenientes da utilização de ROMs, os fabricantes de circuitos integrados conceberam dispositivos programáveis (PLDs), com restrições ao nível de:

- Nº de entradas (n)

- Nº de portas AND (p)

- Nº de portas OR (q)

Prof. Nuno Roma

Sistemas Digitais 2015/16

#### ■ PLA: Programmable Logic Array

- Para ultrapassar os inconvenientes da utilização de ROMs, os fabricantes de circuitos integrados conceberam dispositivos programáveis (PLDs), com restrições ao nível de:

- Nº de entradas (n)

- Nº de portas AND (p)

- Nº de portas OR (q)

#### ► Consequências:

- Cada uma das q funções tem de ser expressa numa soma de produtos;

- O número total de <u>implicantes disponíveis</u> não pode ultrapassar p.

► Estas restrições não existem nas ROMs, pois todos os mintermos estão disponíveis nas saídas do descodificador interno da ROM.

Prof. Nuno Roma

Sistemas Digitais 2015/16

15

## **Programmable Logic Array (PLA)**

Prof. Nuno Roma

Sistemas Digitais 2015/16

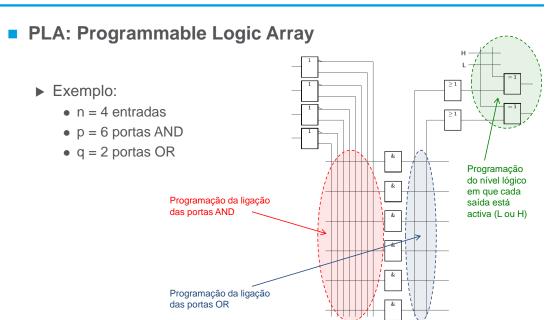

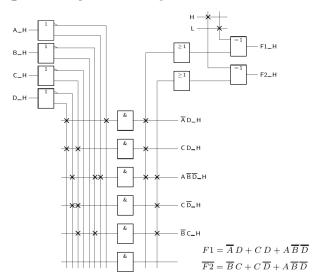

#### ■ PLA: Programmable Logic Array – Exemplo

#### ▶ Exemplo:

- n = 4 entradas

- p = 6 portas AND

- q = 2 portas OR

#### Tabela de Verdade

| A_H | B_H | C_H | D_H | F1_H | F2_H |

|-----|-----|-----|-----|------|------|

| L   | L   | L   | L   | L    | Н    |

| L   | L   | L   | H   | Н    | H    |

| L   | L   | H   | L   | L    | L    |

| L   | L   | H   | H   | Н    | L    |

| L   | H   | L   | L   | L    | H    |

| L   | H   | L   | H   | Н    | H    |

| L   | H   | H   | L   | L    | L    |

| L   | H   | H   | H   | Н    | H    |

| H   | L   | L   | L   | Н    | L    |

| H   | L   | L   | H   | L    | H    |

| H   | L   | H   | L   | Н    | L    |

| H   | L   | H   | H   | Н    | L    |

| H   | H   | L   | L   | L    | H    |

| H   | H   | L   | H   | L    | H    |

| H   | H   | H   | L   | L    | L    |

| H   | H   | H   | H   | H    | H    |

Prof. Nuno Roma

Sistemas Digitais 2015/16

17

## **Programmable Logic Array (PLA)**

### ■ PLA: Programmable Logic

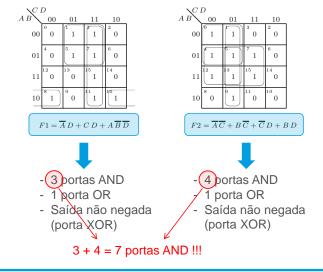

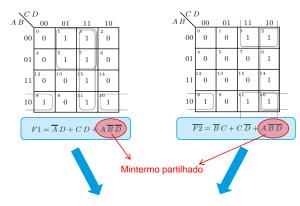

#### ▶ Observação:

Se agruparmos os maxtermos, em vez dos mintermos, obteremos uma expressão mais simples

#### **Problema:**

A PLA n\u00e3o tem estrutura que facilite o uso de produtos de somas

#### ▶ Alternativa:

- Obter a expressão na negação de F2: F2

- Depois nega-se esta negação: F2 = F2

$$F2 = \overline{A}\,\overline{C} + B\,\overline{C} + \overline{C}\,D + B\,D$$

$\overline{F2} = \overline{B}\,C + C\,\overline{D} + A\,\overline{B}\,\overline{D}$

#### ■ PLA: Programmable Logic Array – Exemplo

- ▶ Exemplo:

- n = 4 entradas

- p = 6 portas AND

- q = 2 portas OR

#### Tabela de Verdade

| A_H | в_н | C_H | D_H | F1_H | F2_H |

|-----|-----|-----|-----|------|------|

| L   | L   | L   | L   | L    | Н    |

| L   | L   | L   | H   | Н    | H    |

| L   | L   | H   | L   | L    | L    |

| L   | L   | H   | H   | Н    | L    |

| L   | H   | L   | L   | L    | H    |

| L   | H   | L   | H   | Н    | H    |

| L   | H   | H   | L   | L    | L    |

| L   | H   | H   | H   | Н    | H    |

| Н   | L   | L   | L   | Н    | L    |

| Н   | L   | L   | H   | L    | H    |

| H   | L   | H   | L   | Н    | L    |

| H   | L   | H   | H   | Н    | L    |

| Н   | H   | L   | L   | L    | H    |

| Н   | H   | L   | H   | L    | H    |

| H   | H   | H   | L   | L    | L    |

| H   | H   | H   | H   | Н    | H    |

|     |     |     |     |      |      |

- 5 portas AND

- 2 porta OR

- 1 saída não negada (F1)

- 1 saída negada (F2)

Prof. Nuno Roma

Sistemas Digitais 2015/16

19

OK!

# **Programmable Logic Array (PLA)**

### ■ PLA: Programmable Logic Array – Exemplo

- ▶ Exemplo:

- n = 4 entradas

- p = 6 portas AND

- q = 2 portas OR

#### Tabela de Verdade

| 100000000000000000000000000000000000000 |     |     |     |      |      |  |

|-----------------------------------------|-----|-----|-----|------|------|--|

| A_H                                     | в_н | C_H | D_H | F1_H | F2_H |  |

| L                                       | L   | L   | L   | L    | Н    |  |

| L                                       | L   | L   | H   | Н    | H    |  |

| L                                       | L   | H   | L   | L    | L    |  |

| L                                       | L   | H   | H   | Н    | L    |  |

| L                                       | H   | L   | L   | L    | H    |  |

| L                                       | H   | L   | H   | Н    | H    |  |

| L                                       | H   | H   | L   | L    | L    |  |

| L                                       | H   | H   | H   | Н    | H    |  |

| Н                                       | L   | L   | L   | Н    | L    |  |

| H                                       | L   | L   | H   | L    | H    |  |

| H                                       | L   | H   | L   | Н    | L    |  |

| H                                       | L   | H   | H   | Н    | L    |  |

| н                                       | H   | L   | L   | L    | Н    |  |

| Н                                       | H   | L   | H   | L    | H    |  |

| H                                       | H   | H   | L   | L    | L    |  |

| Н                                       | H   | H   | H   | Н    | H    |  |

Prof. Nuno Roma Sistemas Digitais 2015/16

#### ■ PLA: Programmable Logic Array

- ► Exemplo: PLS100 (Philips)

- 16 entradas

- p = 48 portas AND

- q = 8 portas OR

Prof. Nuno Roma

Sistemas Digitais 2015/16

21

# **Programmable Logic Array (PLA)**

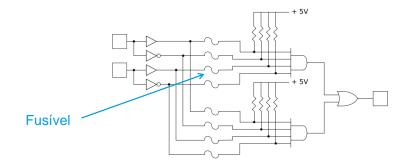

### Programação

- ► One-Time-Programming (OTP) podem ser programados apenas uma única vez

- Aquando da programação, existem fusíveis que são "queimados" e que irão definir os operandos de cada **mintermo**.

Prof. Nuno Roma

Sistemas Digitais 2015/16

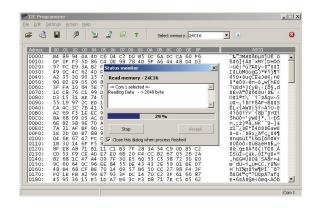

### Programação

▶ O programador está ligado a um computador (PC), que lê um ficheiro com a tabela de verdade pretendida para o circuito

Prof. Nuno Roma

Sistemas Digitais 2015/16

23

### **ROMs vs PLAs**

#### ROMs vs PLAs

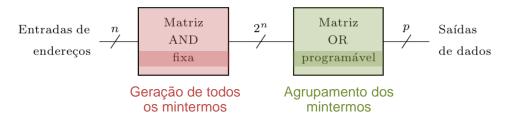

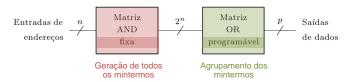

No caso das ROMs, as ligações das portas AND estão <u>fixas</u> e é possível <u>programar</u> as ligações das portas OR:

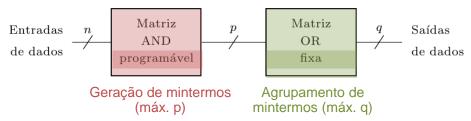

No caso das PLAs, tanto as ligações das portas AND como as ligações das portas OR são <u>programáveis</u>:

Prof. Nuno Roma

Sistemas Digitais 2015/16

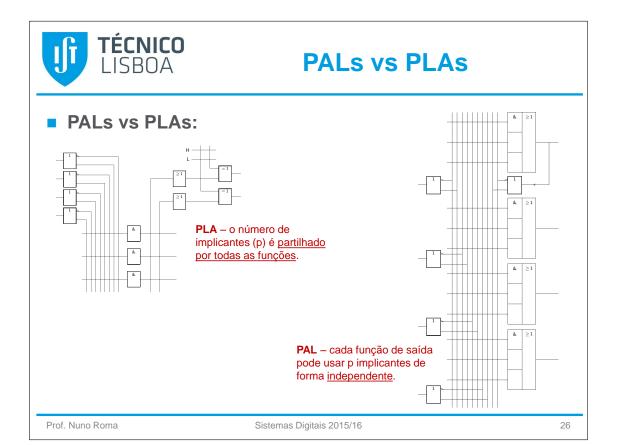

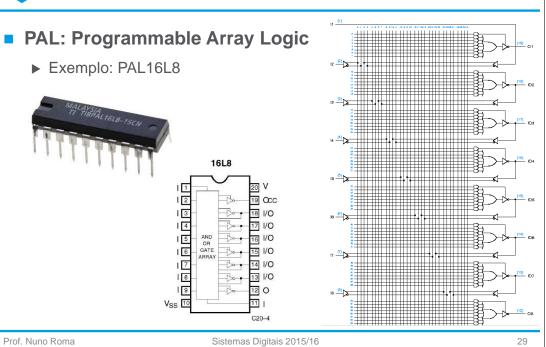

### **Programmable Array Logic (PAL)**

#### ■ PAL: Programmable Array Logic

No caso das PALs, as ligações entre as portas AND e as portas OR estão <u>fixas</u>, e apenas é possível programar as ligações das portas AND às entradas:

#### ▶ Restrições:

- Cada uma das q funções tem de ter a forma de uma soma de produtos;

- O número de implicantes da soma não pode exceder p <u>por função</u> (numa PLA, o número de implicantes (p) é <u>partilhado por todas as funções</u>).

Prof. Nuno Roma Sistemas Digitais 2015/16 25

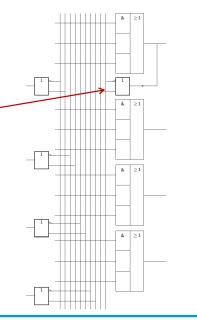

### **Programmable Array Logic (PAL)**

### ■ PAL: Programmable Array Logic

- Uma das linhas de saída pode ser realimentada para o interior da PAL, para permitir construir funções que necessitem de um maior número de portas AND.

- Algumas PALs incluem também flipflops nas saídas, de modo a permitir realizar circuitos sequenciais.

Prof. Nuno Roma

Sistemas Digitais 2015/16

27

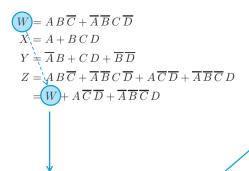

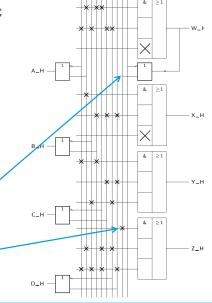

# **Programmable Array Logic (PAL)**

► Exemplo:

Realimentação da saída da função W (que corresponde, também, a mintermos da função Z), a fim de alargar o número de operandos da porta AND.

Prof. Nuno Roma

Sistemas Digitais 2015/16

### **Programmable Array Logic (PAL)**

# Field-Programmable Gate Array (FPGA)

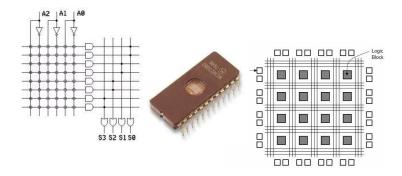

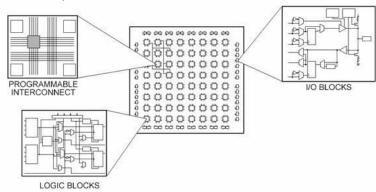

### ■ FPGA: Field-Programmable Gate Array

Dispositivo constituído por uma grelha com milhares de blocos lógicos programáveis interligados entre si (CLB: Configurable Logic Blocks), em que cada bloco implementa uma função booleana simples:

Prof. Nuno Roma

Sistemas Digitais 2015/16

# Field-Programmable Gate Array (FPGA)

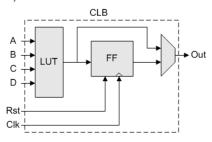

#### Configurable Logic Block (CLB)

- ► Pode ser constituído por:

- **Look-Up Table (LUT)**, semelhante a uma ROM, que permite definir uma qualquer **função combinatória** arbitrária de *n* entradas

- Elemento de memória (ex: **Flip-Flop**), ligado à saída da LUT, que permite a realização de **circuitos sequenciais**.

- ► Exemplo (simples):

Prof. Nuno Roma Sistemas Digitais 2015/16

# Field-Programmable Gate Array (FPGA)

### ■ FPGA: Field-Programmable Gate Array

- ▶ A programação/configuração é feita aquando do ciclo de inicialização, em que a FPGA lê um ficheiro de configuração (.bit) a partir de uma ROM externa, a fim de <u>configurar</u>:

- LUTs de todos os CLBs;

- MUXs de saída de todos os CLBs:

- Interligações entre CLBs;

- Memórias internas;

- Interface com o exterior (I/O).

- Pode ser configurada múltiplas vezes!

Prof. Nuno Roma

Sistemas Digitais 2015/16

32

# Field-Programmable Gate Array (FPGA)

### ■ FPGA: Field-Programmable Gate Array

- ▶ O grande número de CLBs (>10<sup>6</sup>) actualmente disponibilizados por FPGAs de última geração permite a integração e implementação, num único chip, de:

- Vários processadores (sistemas multi-core)

- Processadores Digitais de Sinal (DSP)

- Micro-controladores

- Memórias, etc.

#### ► Programação:

- Dada a elevada complexidade dos circuitos envolvidos, estes dispositivos são geralmente programados através de linguagens de descrição de circuitos (*Hardware Description Languages – HDL*):

- o VHDL

- o Verilog

Prof. Nuno Roma

Sistemas Digitais 2015/16

33

#### **VHDL**

### VHDL (VHSIC Hardware Description Language)

► Exemplo 1: multiplexer 2:1

```

entity MUX is

port (

A : in std_logic;

B : in std_logic;

Sel : in std_logic;

Out : out std_logic;

Out entity MUX;

architecture RTL of MUX is

begin

Out <= A when Sel = '1' else B;

end architecture RTL;</pre>

```

Prof. Nuno Roma

Sistemas Digitais 2015/16

### **VHDL**

### VHDL (VHSIC Hardware Description Language)

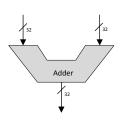

► Exemplo 2: somador binário

```

entity ADDER is

generic (

WIDTH: in natural := 32);

port (

OP1 : in std_logic_vector(WIDTH-1 downto 0);

OP2 : in std_logic_vector(WIDTH-1 downto 0);

SUM : out std_logic_vector(WIDTH-1 downto 0));

end entity ADDER;

architecture RTL of ADDER is

begin

SUM <= OP1 + OP2;

end architectore RTL;</pre>

```

NOTA: esta descrição (comportamental) não é permitida para a realização dos trabalhos de laboratório de "Sistemas Digitais"

Prof. Nuno Roma

Sistemas Digitais 2015/16

35

### **VHDL**

### VHDL (VHSIC Hardware Description Language)

► Exemplo 3: flip-flop tipo D

```

entity FLIP_FLOP is

port (

RST : in std_logic;

CLK : in std_logic;

D : in std_logic;

Q : out std_logic;

end entity FLIP_FLOP;

architecture RTL of FLIP_FLOP is

begin

process(RST, CLK)

begin

if RST = '1' then

Q <= '0';

elsif rising_edge(CLK) then

Q <= D;

end if;

end process;

end architecture RTL;</pre>

```

Prof. Nuno Roma

Sistemas Digitais 2015/16

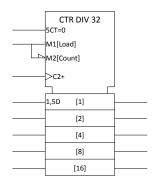

### **VHDL**

### VHDL (VHSIC Hardware Description Language)

#### ► Exemplo 4:

Contador binário

```

entity COUNTER is

generic (

WIDTH : in natural := 5);

port (

RST : in std_logic;

CLK : in std_logic;

LOAD : in std_logic;

DATA : in std_logic_vector(WIDTH-1 downto 0);

Q : out std_logic_vector(WIDTH-1 downto 0));

end entity COUNTER;

architecture RTL of COUNTER is

signal CNT : unsigned(WIDTH-1 downto 0);

begin

process(RST, CLK) is

begin

if RST = '1' then

CNT <= (others => '0');

elsif rising_edge(CLK) then

if LOAD = '1' then

CNT <= unsigned(DATA);

else

CNT <= CNT + 1;

end if;

end if;

end process;

Q <= std_logic_vector(CNT);</pre>

```

Prof. Nuno Roma

Sistemas Digitais 2015/16

37

**FIM ???**

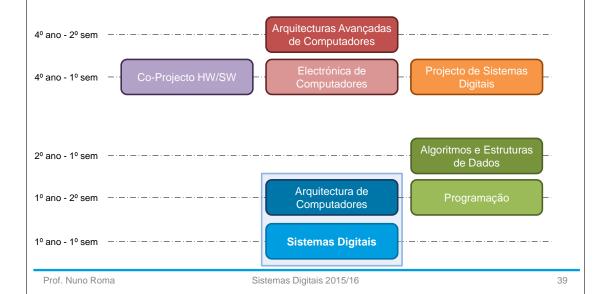

### **Enquadramento no Curso (MEEC)**

### Enquadramento da Disciplina no Curso (MEEC)

### **Próxima Aula**

#### Tema da Próxima Aula:

▶ Série de Problemas P6 – 1ª parte

### Agradecimentos

Algumas páginas desta apresentação resultam da compilação de várias contribuições produzidas por:

- Guilherme Arroz

- Horácio Neto

- Nuno Horta

- Pedro Tomás

Prof. Nuno Roma

Sistemas Digitais 2015/16