# Arquitetura de Computadores

MiEI – 2016/17 DI-FCT/UNL Aula 17

AC - 2016/2017

1

### Desempenho dos sistemas

- Um sistema tem melhor desempenho que outro se produzir resultados em menos tempo

- A melhoria introduzida num sistema (speedup) é dada por:

S = tempo antigo / novo tempo

■ exemplo: um programa passou a executar em 5s quando antes executava em 6s:

S = 6/5 = 1,2 (corresponde a 1,2x mais rápido)

■S = 1 significa que não há alteração

■S = 2 significa que passou a metade do tempo

AC - 2016/2017

## Influência dos componentes

- Componentes software:

- Programa (algoritmos e estruturas de dados), linguagens, bibliotecas, S.O., etc...

- Componentes hardware:

- ■CPU, Memória, Buses, Periféricos, etc...

- Então... exemplo:

- ■Um programa não executa 2x mais rápido só porque usamos um CPU 2x mais rápido!

- ■O *speedup* obtido será proporcional ao tempo de execução do CPU no tempo total do programa...

- os tempos de espera pela memória, periféricos, etc. mantém-se

AC - 2016/2017

3

### Exemplo – o que é melhor?

Considere um sistema que distribui o tempo total de execução nas actividades A e B:

A B

Se actividade B é tornada 5x mais rápida:

Se actividade A é tornada 2x mais rápida:

AC - 2016/2017

### Na arquitectura de computadores

Procura-se optimizar os vários componentes na medida do respectivo peso nos tempos de execução dos nossos sistemas

AC - 2016/2017

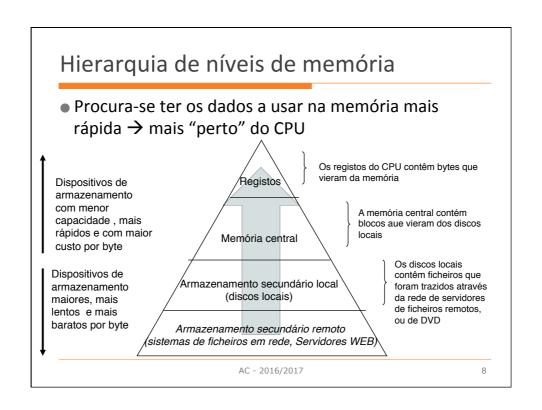

### Migração dos dados para "cima"

- Porquê de usar registos? Porque não executar sempre em memória?

- Porquê trazer os programas para memória? Porque não executar diretamente do disco?

- Desempenho vs. possibilidade tecnológica e custos

- O SO tenta trazer para memória o que está no disco

As aplicações e os dados que as aplicações leem

- O código nos programas procura tirar o melhor partido dos registos

- ■Variáveis são copiadas para os registos

AC - 2016/2017

9

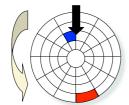

# Operação do disco (Visão de 1 só prato) A superfície do disco gira a velocidade constante A cabeça de leitura e escrita está fixa à ponta de um braço e voa sobre a superfície graças a uma fina almofada de ar. Movendo-se radialment, o braço pode posicionar a cabeça de leitura / escrita sobre qualquer pista

### Acesso ao disco

Cabeça em posição sobre uma pista

AC - 2016/2017

11

# Acesso ao disco

Rotação constante em sentido contrário aos ponteiros do relógio

AC - 2016/2017

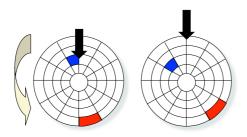

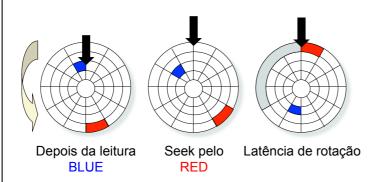

# Acesso ao disco – Leitura

### Prestes a ler o sector azul

AC - 2016/2017

13

# Acesso ao disco – Leitura

Após ler o sector azul

AC - 2016/2017

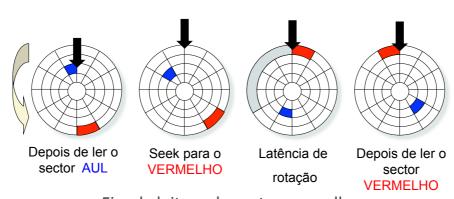

### Acesso ao disco – Leitura

Próximo sector a ler é o sector vermelho (noutra pista)

AC - 2016/2017

15

# Acesso ao disco - Seek

Deslocamento (Seek) para a pista do sector vermelho

AC - 2016/2017

# Acesso ao disco – latência de rotação

Esperar que o setor vermelho apareça debaixo da cabeça

AC - 2016/2017

17

### Acesso ao disco - Leitura

Fim da leitura do sector vermelho

AC - 2016/2017

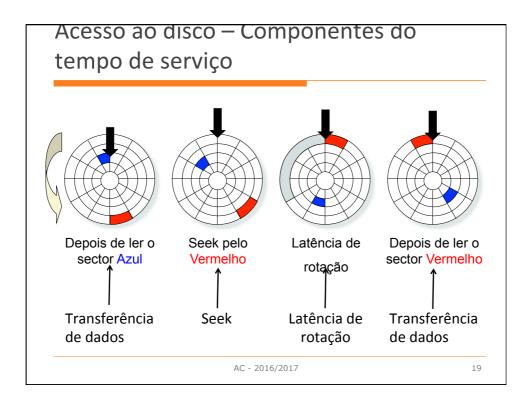

### Tempo de acesso a um setor

Tempo médio para acesso a um dado sector pode ser aproximado por:

Tacesso = Tmédio seek + Tmédio de rotação + Tmédio de transferência

- Tempo de seek (Tmédio seek)

- Tempo para posicionar a cabeça sobre a pista pretendida.

- ■Típico: 3 9 ms

- Latência de rotação(Tmédio rotação)

- Tempo de espera até que o 1º bit do sector pretendido passe debaixo da cabeça de r/w.

- ■Tmédio de rotação = ½ 60/RPMs

- ■Típica velocidade de rotação = 7200 RPMs → 4ms

- Tempo de transferência (Tmédio transferência)

- Tempo para ler os bits do sector pretendido.

- Tmédio de transferênca = (1/(média # sectors/pista)) 60/RPM

AC - 2016/2017

### Exemplo de cálculo de tempo de acesso

- Dados:

- ■Velocidade de rotação = 7200 RPM

- ■Tempo médio de seek = 9 ms.

- No. médio de setores/pista = 400.

- Determina-se:

- ■Tmédio de rotação = 1/2x(60/7200 RPM) = 4 ms.

- ■Tmédio de transferência = 1/400 sets/pista x 60/7200 RPM= 0,02 ms

- ■Taccesso = 9 ms + 4 ms + 0.02 ms

- Pontos importantes:

- Tempo de acesso dominado pelo seek time e pela latência de rotação.

- 1º bit de um sector é o que demora mais, o resto é de "graça".

- Acesso a sectores consecutivos poupam no seek e rotação

- O disco pode ser 100 000x mais lento que a memória central

AC - 2016/2017

21

# Blocos lógicos no disco

- Os discos modernos apresentam uma versão abstracta e simplificada da geometria do disco:

- ■Os sectores disponívies são vistos como uma sequência de blocos lógicos (0, 1, 2, ...)

- ■LBA Logical block addressing

- Mapeamento entre blocos lógicos e blocos físicos

- Mantido por hardware/firmware no controlador do disco

- Converte pedidos de blocos lógicos em triplos ordenados (superfície, pista, sector).

AC - 2016/2017

| Tendências                                |                       |                     |                   |                                 |                       |                       |                         |                                    |  |  |  |

|-------------------------------------------|-----------------------|---------------------|-------------------|---------------------------------|-----------------------|-----------------------|-------------------------|------------------------------------|--|--|--|

| Métrica                                   | 1980                  | 1985                | 1990              | 1995                            | 2000                  | 2005                  | 2010 2                  | 2010:1980                          |  |  |  |

| \$/MB<br>access (ns)                      | 19 200<br>300         | 2 900<br>150        | 320<br>35         | 256<br>15                       | 100<br>3              | 75<br>2               | 60<br>1.5               | 320x<br>200x                       |  |  |  |

| DRAM                                      |                       |                     |                   |                                 |                       |                       |                         |                                    |  |  |  |

| Metric                                    | 1980                  | 1985                | 1990              | 1995                            | 2000                  | 2005                  | 2010 2010:1980          |                                    |  |  |  |

| \$/MB<br>access (ns)<br>typical size (MB) | 8 000<br>375<br>0.064 | 880<br>200<br>0.256 | 100<br>100<br>4   | 30<br>70<br>16                  | 1<br>60<br>64         | 0.1<br>50<br>2 000    | 0.06<br>40<br>8 000     | 130 000x<br>9x<br>125 000x         |  |  |  |

| Disk                                      |                       |                     |                   |                                 |                       |                       |                         |                                    |  |  |  |

| Metric                                    | 1980                  | 1985                | 1990              | 1995                            | 2000                  | 2005                  | 2010 2                  | 2010:1980                          |  |  |  |

| \$/MB<br>access (ms)<br>typical size (MB) | 500<br>87<br>1        | 100<br>75<br>10     | 8<br>28<br>160 AC | 0.30<br>10<br>- <b>200</b> 0201 | 0.01<br>8<br>7 20 000 | 0.005<br>4<br>160 000 | 0.0003<br>3<br>1 500 00 | 1 600 000x<br>29x<br>00 1 500:000x |  |  |  |

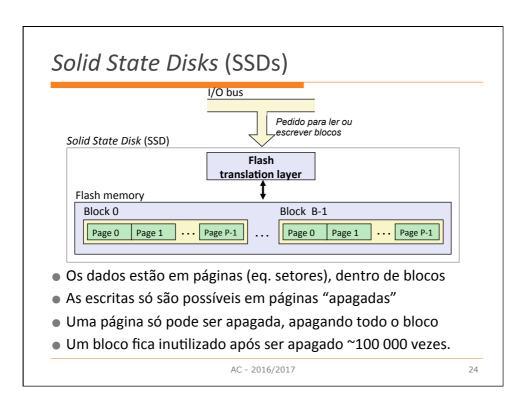

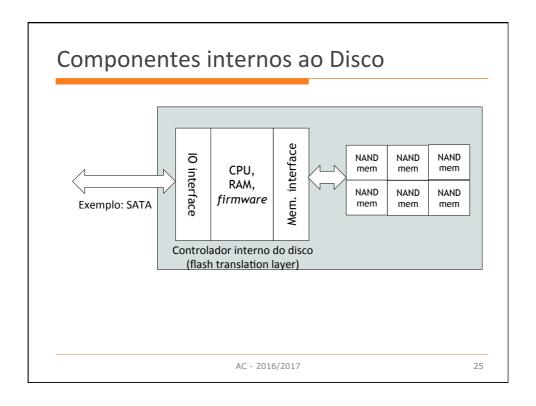

### Solid State Disks (SSDs)

Leituras sequenciais 300 MB/s Escritas sequenciais 250 MB/s Leituras aleatórias 170 MB/s Escritas aleatéorias 70 MB/s Tempo de acesso leitura 20µs Tempo de acesso escrita 200µs

- A escrita de uma página pode exigir apagar o bloco

- Apagar um bloco é lento (cerca de 1 ms)

- A escrita de uma página pode desencadear a cópia de todas as páginas em uso no bloco:

- 1. Escolher um bloco livre e apagá-lo se necessário

- 2. Copiar as páginas a manter do bloco antigo para o novo

- 3. Escrever a página nesse bloco

- 4. Marcar o bloco antigo como livre

- Esta gestão é feita pelo firmware interno ao disco

AC - 2016/2017

## Comparação entre SSD e discos magnéticos

- Vantagens

- ■Sem partes móveis → maior rapidez e robustez, menos consumo

- Desvantagens

- ■Tem o potencial para se gastarem

- Minimizado pela "wear leveling logic" na flash translation layer

- E.g. Intel X25 garante 1 petabyte (1015 bytes) de escritas aletórias até que o disco se torne inútil

- ■100 x mais caro por byte (tem vindo a diminuir)

AC - 2016/2017

### Localidade

- Princípio da localidade: Os programas têm padrões conhecidos de acesso a memória

- ■Localidade temporal: items referenciados recentemente tendem a voltar a sê-lo.

sum = 0;

return sum;

for (i = 0; i < n; i++)

sum += a[i];

■Localidade espacial: items com endereços próximos tendem a ser referenciados em conjunto.

### Exemplo:

- · Dados

- Elementos do array são referenciados em sequência: Localidade espacial

- sum referenciado em cada iteração:

- Instruções Localidade temporal

- Instruções referenciadas em sequência: Localidade espacial

- -Ciclo: Localidade temporal

AC - 2016/2017

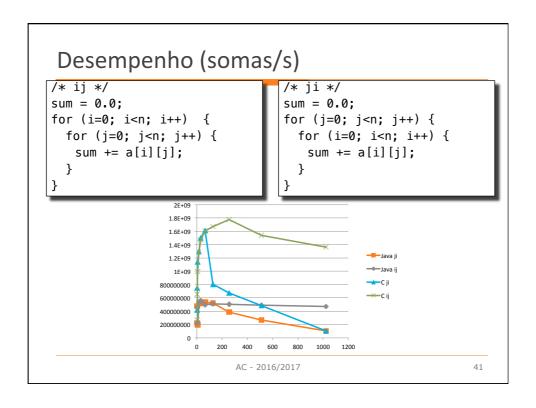

### Localidade (1)

• Esta função tem boa localidade?

```

int sumarrayrows(int a[M][N])

{

int i, j, sum = 0;

for (i = 0; i < M; i++)

for (j = 0; j < N; j++)

sum += a[i][j];

return sum;

}</pre>

```

Resposta: Sim. Os compiladores de C guardam as matrizes, na memória, linha a linha. Neste caso o percurso na matriz é feito linha a linha. Portanto faz-se sempre acesso a posições de memória contíguas.

AC - 2016/2017

31

# Localidade (2)

• Esta função tem boa localidade?

```

int sumarraycols(int a[M][N])

{

int i, j, sum = 0;

for (j = 0; j < N; j++)

for (i = 0; i < M; i++)

sum += a[i][j];

return sum

}</pre>

```

Resposta: Não. Neste caso o percurso da matriz é feito coluna a coluna; a sequência é a[0][0], a[1][0] ..., a[M][0], a[0][1] ... Portanto dois acessos consecutivos não fazem acesso a posições de memória contíguas.

AC - 2016/2017

### Tecnologia de memória

- Todas as memórias rápidas são baseadas em semicondutores

- Dynamic Random Access Memory (DRAM)

- ■DRAM oferece a melhor relação preço/desempenho, mas necessita de refrescamento periodicamente e após cada leitura

- Static Random Access Memory (SRAM)

- ■SRAM é mais rápida mas muito mais cara, consome mais energia e ocupa mais espaço

- A memória RAM dos computadores é DRAM

AC - 2016/2017

33

### Sumário SRAM vs DRAM

|      | Transistores por bit | Tempo<br>acesso | Precisa refresh? | Custo | Utilização                     |

|------|----------------------|-----------------|------------------|-------|--------------------------------|

| SRAM | 4 or 6               | 1X              | Não              | 100x  | Memória cache                  |

| DRAM | 1                    | 10X             | Sim              | 1X    | Memória central, frame buffers |

DRAM e SRAM são memória volátil

■Perdem informação se a energia é desligada.

AC - 2016/2017

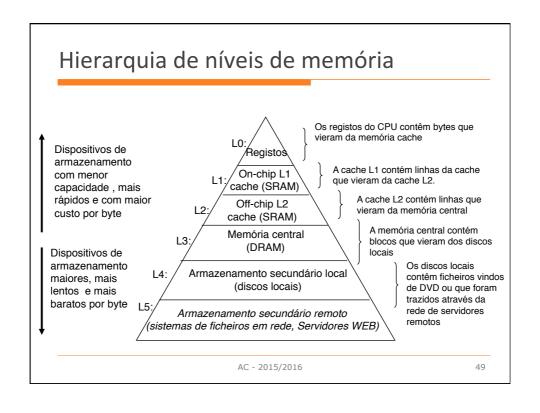

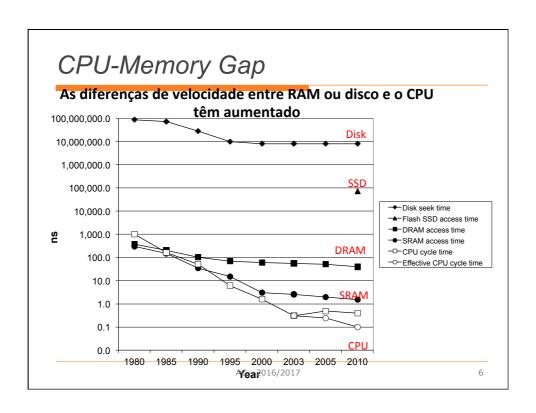

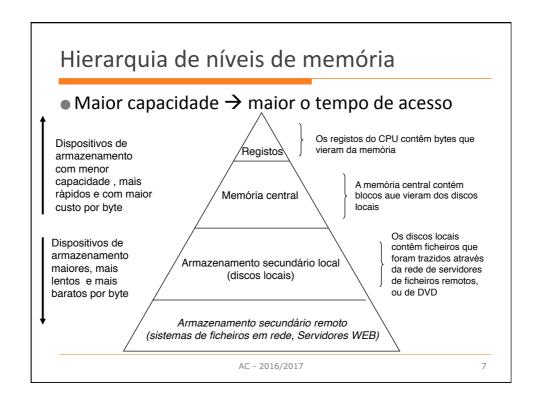

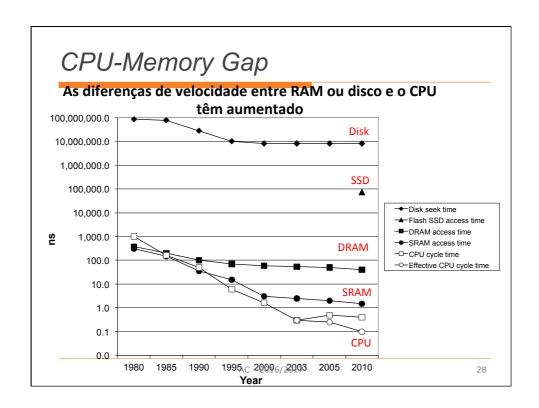

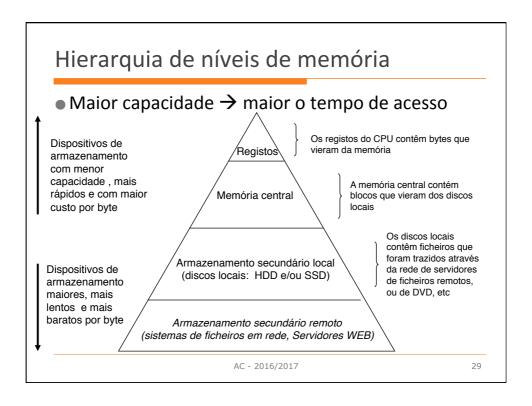

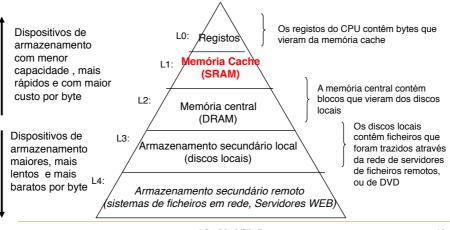

### Hierarquia de memória

- Propriedades fundamentais:

- As tecnologias mais rápidas custam mais por byte e têm menor capacidade.

- ■O fosso entre o CPU e a memória central está a aumentar.

- ■Os bons programas têm boa localidade.

- Estas propriedades suportam:

- abordagem do armazenamento como uma hierarquia de memória

- ■Introduzir mais um nível de memória para tirar partido da localidade: queremos memória central DRAM com o desempenho da SRAM

AC - 2016/2017

35

### Hierarquia de níveis de memória

Poderemos ter mais um nível para que o programa que está a executar seja mais rápido?

AC - 2016/2017

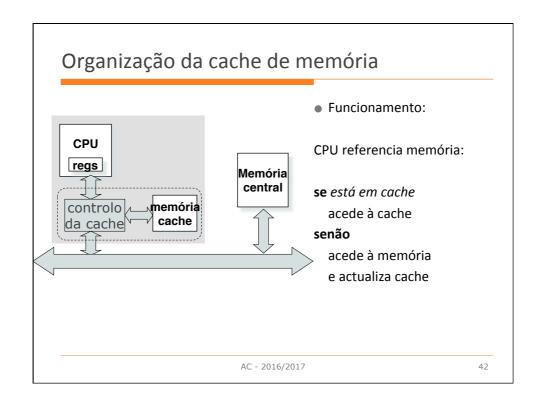

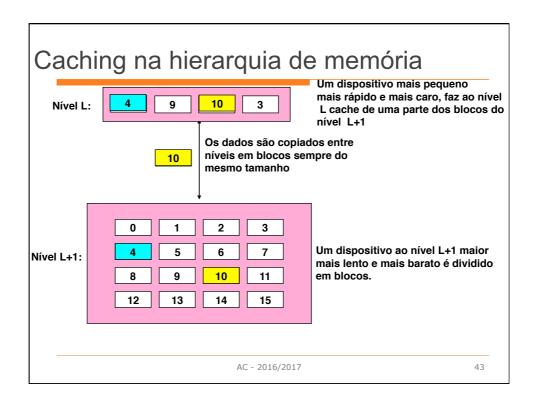

### Ideia da Cache

- Cache: Um dispositivo "invisível" que atua como zona temporária para armazenamento de dados de outro dispositivo mais lento mas maior.

- Ideias fundamentais:

- ■No nível L, o dispositivo menor e mais rápido, guarda parte do conteúdo do dispositivo maior e mais lento do nível L+1

- ■Baseado na localidade, procura-se ter no nível L os dados de L+1 mais prováveis de ser brevemente usados

- ■A atualização dos dados em L deve ser transparente para o utilizador desse nível

AC - 2016/2017

37

### Utilização da ideia

- O mesmo princípio é explorado a outros níveis

- Exemplo dos browsers Web:

- ■Procuram manter no disco local os dados remotos

- ■Mantém em memória os dados que estão a usar ou que podem vir a usar brevemente

AC - 2016/2017

### Ideia da Cache

- Vantagens esperadas:

- ■A localidade leva a que a maior parte dos acessos (leitura/escrita) sejam aos dados já no nível L em vez de ter de ao nível L+1.

- ■O armazenamento no nível L+1 pode ser mais lento, e assim mais barato e muito maior.

- ■Efeito global: Um grande conjunto de memória que custa o preço da que se encontra no nível mais baixo, mas que permite o acesso aos dados a um ritmo semelhante à do nível mais elevado.

AC - 2016/2017

39

### Hierarquia de níveis de memória

Poderemos ter um, 2, ou 3 níveis de memória cache, gerida pelo hardware

AC - 2016/2017

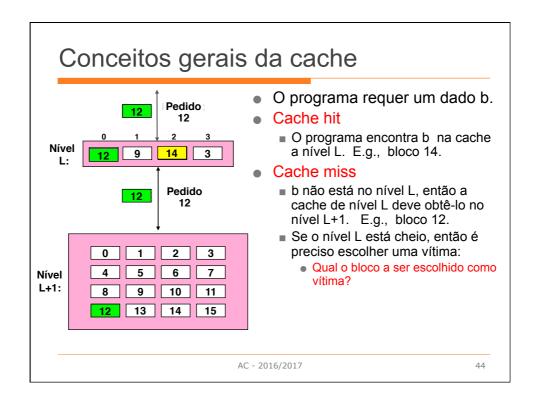

### Conceitos gerais da cache: hit/miss

### Cache hit

O programa encontra o dado pretendido na cache (nível L). Não é preciso fazer nada!

### Cache miss

- Não enconta o que pretende no nível L, então a cache de nível L deve obtê-lo no nível L+1 (e assim sucessivamente).

- Se o nível L está cheio, então é preciso arranjar espaço, escolhendo uma vítima:

- Qual o bloco a ser escolhido como vítima (ao acaso? LRU least recently used?)

- Se o bloco vítima está limpo, isto é, não foi alterado desde que veio para o nível L, posso carregar o novo bloco por cima

- Se o bloco vítima está sujo, isto é, foi alterado, é preciso escrevê-lo no nível L+1 antes de o substituir

AC - 2016/2017

45

### Conceitos gerais duma cache

- Taxa de sucesso (hit ratio)

- h = percentagem de vezes que o dado pretendido está na cache:

h = núm. cache hit / núm. total acessos

- Tempo de acesso médio:

- lacksquare  $T_L$  é o tempo de acesso no nível L

- T<sub>I+1</sub> é o tempo de acesso no nível L+1

- Tempo de acesso médio: Ta

$$Ta = h * T_L + (1 - h) * T_{L+1}$$

AC - 2016/2017

- Exemplo:

- T cache = 2 ns

- $\blacksquare T mem = 8 ns$

- **■***Hit ratio* = 80%

- Ta =  $h * T_L + (1 h) * T_{L+1}$ • Ta = 0,8 x 2 + 0,2 x 8 = **3,2** ns

AC - 2016/2017

47

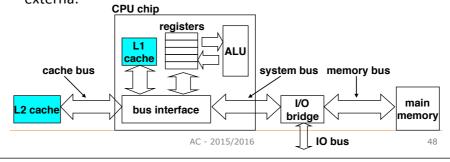

# Cache – Exemplo com dois níveis

- Cache são memórias rápidas (SRAM) geridas automaticamente pelo hardware.

- CPU procura em L1, depois em L2, finalmente na memória central

- Podem introduzir algum *overhead*, mas desprezável

- Exemplo de arquitetura com L1 interna ao chip do CPU e L2 externa: