Mestrado Integrado em Engenharia Informática – Arquitetura de Computadores – 2013/14

Segundo teste – 30 de maio de 2014 – Duração 1 hora e 30 minutos

Responda às questões no espaço reservado para o efeito após cada alínea, ou na última página caso necessite mais espaço. Apresente todos os cálculos que efectuar, e esclareça qualquer pressuposto que tenha de fazer para resolver uma questão. Qualquer caso de fraude ou plágio será punido com a reprovação à disciplina, de acordo com os regulamentos em vigor.

| -   |        |       |

|-----|--------|-------|

| г   |        |       |

|     | A 1 /  | N 1   |

| - 1 | Número | INAMA |

| - 1 |        | Nome  |

|     |        |       |

## Grupo I (10 valores)

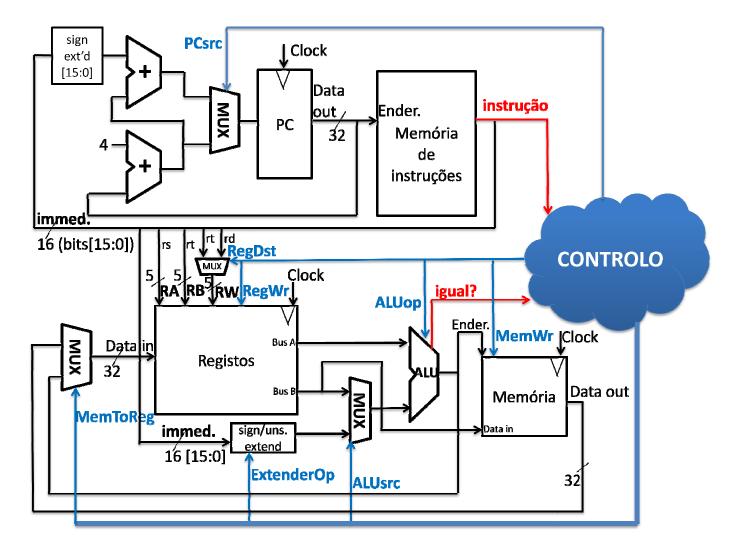

1. Pretende-se adicionar ao conjunto de instruções do MIPS uma instrução chamada **loadSum** que efectua a soma entre um valor lido da memória e um valor imediato, armazenando o resultado num registo.

A especificação da instrução "loadSum rt, rs, imed" é a seguinte:

```

$pc ← $pc + 4

R[rt] ← MEM[rs] + ext_sinal(imed)

```

a) Qual o formato (R, I, ou J) da nova instrução em linguagem máquina MIPS? Justifique brevemente.

- b) Para suportar esta instrução, quais as alterações que são necessárias efectuar ao hardware do CPU de ciclo único? Deverá em particular indicar quais os componentes novos que têm de ser adicionados ou modificados. Pode adicionar multiplexers e fios, mas não pode adicionar novos somadores. A resposta está dividida em três partes:

- b.1) Efectue as alterações directamente no circuito seguinte.

b.2) Liste os componentes que foram adicionados e modificados, e para cada componente indique claramente a que entradas ou saídas de outros componentes estão ligados.

| b.3 | 3) Liste as novas linhas de controlo que foram adicionadas. |

|-----|-------------------------------------------------------------|

c) Qual é o valor para todas as linhas de controlo do CPU quando esta instrução estiver a ser executada? Deve indicar o valor da respectiva linha (0 ou 1) ou X no caso de ser indiferente ("don't care"). Deve também adicionar à tabela abaixo as novas linhas de controlo ou indicar as alterações que fez nas linhas existentes.

| Número: | Nome: |  |  |  |  |

|---------|-------|--|--|--|--|

|---------|-------|--|--|--|--|

| PCSrc            | RegDst               | RegWr           | ALUsrc                | MemWr          |

|------------------|----------------------|-----------------|-----------------------|----------------|

| 0=PC+4;          | 0=rt (bits [20:16]); | 0=Não escrever; | 0=RegB;               | 0=Não escrever |

| 1=PC+4+(sign_ext | 1=rd (bits [15:11])  | 1=escrever      | 1=imediato (bits      | 1=escrever     |

| (immed)<<2)      |                      | (registo RW)    | menos signif. instr.) | (memória)      |

| valor:           |                      |                 |                       |                |

| MemToReg                  | ExtenderOp                      | ALUop                               |  |

|---------------------------|---------------------------------|-------------------------------------|--|

| 0=da ALU;<br>1=da memória | 0=zero extend;<br>1=sign extend | 00=ADD; 01=SUB;<br>10=OR;11=COMPARE |  |

|                           |                                 |                                     |  |

| d) | "pipelini                                                                                                                                                                                                                | ·                                                                    | e introduzir esta nova<br>s na cadeira? (Escolha<br>)                                                                              | •                                                                                       |                    |       |  |  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------|-------|--|--|

|    | patamai<br>∐ Altera<br>∐ Altera<br>∐ Altera                                                                                                                                                                              | res, podendo tal afe<br>a, pois pode gerar n<br>a, pois a ordem de e | o CPU com pipelining, etar ou não a duração do ovos conflitos de contro execução dos patamares a frequência do CPU, po de relógio. | o ciclo de relógio.<br>No ( <i>control hazards</i> ).<br>( <i>(stages</i> ) é diferente | nesta instrução.   |       |  |  |

|    | ∐ Altera, pois deixa de ser necessário o forwarding para minimizar os conflitos de dados.                                                                                                                                |                                                                      |                                                                                                                                    |                                                                                         |                    |       |  |  |

|    |                                                                                                                                                                                                                          | •                                                                    | é <b>falsa</b> sobre o proto<br>s opções – Respostas er                                                                            |                                                                                         |                    | ulti- |  |  |

|    | interliga<br>∐ Se ur                                                                                                                                                                                                     | ição para determina<br>m processador tem                             | na dada entrada no est<br>ar se algum outro proce<br>uma entrada no esta<br>o mesmo endereço no                                    | ssador quer escrever<br>do "modificado", nei                                            | nesses mesmos dado | s.    |  |  |

|    | ☐ Um <i>store</i> (escrita) para uma entrada que está em cache num estado diferente de inválido é servido inteiramente pela cache, isto é, não necessita nenhuma comunicação pela interligação com outros processadores. |                                                                      |                                                                                                                                    |                                                                                         |                    |       |  |  |

|    |                                                                                                                                                                                                                          |                                                                      | âneo duas entradas e<br>r ambas no estado "par                                                                                     | ·                                                                                       | ·                  | mo    |  |  |

|    | •                                                                                                                                                                                                                        | ada instante, apena                                                  | s um processador pod                                                                                                               |                                                                                         |                    | ado   |  |  |

2.

3. Qual das seguintes métricas de performance é melhorada (ou seja, diminui) através da introdução de *pipelining* comparado com o CPU de ciclo único? (Escolha **apenas uma** das opções – Respostas erradas descontam 1/5 da cotação.)

|                                                                                                                                                                                                  |    | memória até ☐ Tempo méo ☐ Tempo de e ☐ Número to            | tência) de execuç<br>à escrita dos result<br>dio de acesso à me<br>execução de um pr<br>tal de instruções d<br>ência) para trazer d | ados nos i<br>mória (mé<br>ograma.<br>e um prog                            | registos estar co<br>etrica AMAT).<br>rama.                                     | oncluída).                                           |                                                                                   | ão é lida da                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------|

|                                                                                                                                                                                                  |    | <u> Потпро (паст</u>                                        | o                                                                                                                                   |                                                                            | (10 valores)                                                                    |                                                      |                                                                                   |                                                               |

| 4.                                                                                                                                                                                               | Co | nsidere tambéi                                              | rquitetura de um<br>m que esta arquite<br>16 Bytes, e usa um                                                                        | CPU com                                                                    | endereços virtu<br>uma cache de n                                               |                                                      | •                                                                                 | •                                                             |

| <ul> <li>Supondo que a capacidade da cache (ou seja, o total de dade<br/>Bytes, quantos bits são usados para cada campo do ender<br/>Apresente e justifique os cálculos que efectuar.</li> </ul> |    |                                                             |                                                                                                                                     |                                                                            |                                                                                 |                                                      |                                                                                   | -                                                             |

|                                                                                                                                                                                                  |    |                                                             |                                                                                                                                     |                                                                            |                                                                                 |                                                      |                                                                                   |                                                               |

|                                                                                                                                                                                                  | b) | endereços: 24 inicialmente s<br>dos acessos<br>(capacidade, | emente da sua res<br>4 bits para a tag, 4<br>se encontrava vazia<br>seguintes, se é u<br>conflito, ou obriga<br>os campos válido,   | I para o ír<br>a, isto é, to<br>m <i>hit</i> ou<br>tório), se <sub>§</sub> | ndice, e 4 para o<br>odas as entradas<br>um <i>miss</i> , no<br>gera uma escrit | o deslocan<br>s eram inva<br>caso do r<br>a para a m | nento. Supondo<br>álidas, indique, p<br>miss qual é o<br>nemória ( <i>write-b</i> | que a cache<br>para cada um<br>tipo de miss<br>pack) e qual é |

|                                                                                                                                                                                                  |    | hit/miss:<br>write back (sinconteúdo das<br>Índice          | ndereço: ABBA001 m/não): duas primeiras lin válido?                                                                                 | t                                                                          | ipo de miss:<br>]<br>he após o acess                                            | so:<br>dirty                                         |                                                                                   | ]                                                             |

|                                                                                                                                                                                                  |    | 0                                                           |                                                                                                                                     |                                                                            |                                                                                 |                                                      |                                                                                   |                                                               |

|                                                                                                                                                                                                  |    | 2 - Store do e<br>hit/miss:                                 | ndereço: CABE001                                                                                                                    |                                                                            | ipo de miss:                                                                    |                                                      |                                                                                   | ]                                                             |

| Número  | : N                      | Nome:               |                          |                        |

|---------|--------------------------|---------------------|--------------------------|------------------------|

|         |                          |                     |                          |                        |

| ,       | write back (sim/         | não).               |                          |                        |

| ,       | write back (sirriy       | naoj.               |                          |                        |

| (       | conteúdo das du          | uas primeiras linha | as da cache após o acess | 50:                    |

| ĺ       | Índice                   | válido?             | tag                      | dirty                  |

| (       | 0                        |                     |                          |                        |

|         | 1                        |                     |                          |                        |

|         |                          |                     |                          |                        |

| 3       | 3 - Store do end         | ereço: CADA0012     | (hex)                    |                        |

| ŀ       | hit/miss:                |                     | tipo de miss:            |                        |

| ,       | write back (sim/         | não):               |                          |                        |

| ,       | contoúdo das di          | uas primoiras linh  | as da cache após o acess | 50.                    |

| _       | Índice                   | -                   | -                        |                        |

| -       | 0                        | válido?             | tag                      | dirty                  |

|         | 1                        |                     |                          |                        |

|         | •                        |                     |                          |                        |

|         | 4                        | ADD 40040           | /h\                      |                        |

|         |                          | ereço: ABBA0010     |                          |                        |

| ı       | hit/miss:                |                     | tipo de miss:            |                        |

| \       | write back (sim/         | não):               |                          |                        |

| ,       | contoúdo dos du          | uas primairas linh  | as da cache após o acess | -0.                    |

|         | Índice                   | -                   | -                        |                        |

| _       | 0                        | válido?             | tag                      | dirty                  |

|         | 1                        |                     |                          |                        |

| <u></u> | _                        |                     |                          |                        |

| ,       | Г I a a d a a a a d a    |                     | (h a)                    |                        |

|         |                          | ereço: CADA0010     |                          |                        |

| ı       | hit/miss:                |                     | tipo de miss:            |                        |

| ,       | write back (sim/         | não):               |                          |                        |

| ,       | contoúdo das di          | uas primoiras linh  | as da cache após o acess | 50.                    |

| _       | Índice                   | válido?             | -                        |                        |

| _       | 0                        | valluu:             | tag                      | Dirty                  |

|         | 1                        |                     |                          |                        |

|         | •                        |                     |                          |                        |

| c) (    | Oual o <i>hit rate</i> d | esta seguência de   | e acessos? Apresente os  | cálculos que efectuar  |

| σ,      | Quai o merace a          | esta sequentia at   | accessos. Apresente os   | culculos que electual. |

|         |                          |                     |                          |                        |

|         |                          |                     |                          |                        |

|         |                          |                     |                          |                        |

|         |                          |                     |                          |                        |

| L       |                          |                     |                          |                        |

d) Considere a possibilidade de se duplicar a dimensão do bloco, mantendo a capacidade da cache. Estenda esta sequência com mais dois acessos (liste apenas os endereços destes dois acessos

| e) S | e a cache tiv | esse a mesma ca <sub>l</sub> | pacidade (ou seja, mantendo a quantidade total de da    |

|------|---------------|------------------------------|---------------------------------------------------------|

| a    | rmazenáveis ( | em cache) e a di             | mensão do bloco da alínea b), mas fosse associativa     |

|      |               |                              | ica FIFO, qual seria a sequência de hit/miss e o hit ra |

|      | -             | •                            |                                                         |

| R    | esponda preei | nchendo a seguinte           | tabela:                                                 |

| E    | ndereço       | Hit / Miss                   |                                                         |

|      | BBA0010       | ·                            |                                                         |

| С    | ABE0014       |                              |                                                         |

| С    | ADA0012       |                              |                                                         |

| Α    | BBA0010       |                              |                                                         |

| С    | ADA0010       |                              |                                                         |

|      |               |                              | 1                                                       |

| Н    | it rate:      |                              |                                                         |

|      |               |                              |                                                         |

| f)   | A resposta o  | da alínea anterior m         | nudaria se a política fosse LRU em vez de FIFO?         |

|      |               | Sim                          | Não ∐                                                   |

|      |               | _                            | _                                                       |

|      |               |                              |                                                         |